MT9T031C12STC Aptina LLC, MT9T031C12STC Datasheet - Page 22

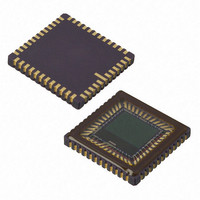

MT9T031C12STC

Manufacturer Part Number

MT9T031C12STC

Description

IC SENSOR IMAGE COLOR 48CLCC

Manufacturer

Aptina LLC

Series

Micron®DigitalClarity®r

Type

CMOS Imagingr

Datasheets

1.MT9T031C12STCH_ES.pdf

(12 pages)

2.MT9T031C12STCH_ES.pdf

(2 pages)

3.MT9T031C12STC.pdf

(2 pages)

4.MT9T031C12STC.pdf

(46 pages)

Specifications of MT9T031C12STC

Pixel Size

3.2µm x 3.2µm

Active Pixel Array

2048H x 1536V

Frames Per Second

12 ~ 93

Voltage - Supply

3 V ~ 3.6 V

Package / Case

48-CLCC

Brief Features

Superior Low Light Performance, Programmable Controls, Low Dark Current, High Frame Rate

Supply Voltage Range

3V To 3.6V

Operating Temperature Range

0°C To +60°C

Ic Function

Digital Image Sensor

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

For Use With

557-1450 - KIT HEAD BOARD FOR MT9T031557-1451 - KIT DEV FOR MT9T031

Lead Free Status / Rohs Status

Compliant

Other names

557-1452

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Part Number:

MT9T031C12STC

Manufacturer:

APTINA

Quantity:

20 000

Table 6:

PDF: 3682685119/Source: 9830567334

MT9T031_DS - Rev.E 5/11 EN

Reg. #

R0x63

R0x64

R0xF8

R0xFF

R100

R248

R255

R99

15:0

Analog calibration offset for red pixels, represented as a two’s complement signed 8-bit value (if bit 8 is clear, the offset is

positive and the magnitude is given by bits 7:0. If bit 8 is set, the offset is negative and the magnitude is given by not([7:0]) +

1). If R0x60[0] = 0, this register is R/O and returns the current value computed by the black level calibration algorithm. If

R0x60[0] = 1, this register is R/W and can be used to manually set the calibration offset.

15:0

Analog calibration offset for blue pixels, represented as a two’s complement signed 8-bit value (if bit 8 is clear, the offset is

positive and the magnitude is given by bits 7:0. If bit 8 is set, the offset is negative and the magnitude is given by not ([7:0]) +

1). If R0x60[0] = 0, this register is R/O and returns the current value computed by the black level calibration algorithm. If

R0x60[0] = 1, this register is R/W and can be used to set the calibration offset manually.

15:0

15:2

1

0

15:0

Chip version.

Core Registers (Continued)

Bits

0x0020

0x0020

0x0001

X

0x0000

0x0001

0x1621

Default

Red Offset (RW)

Blue Offset (RW)

Chip Enable (RW)

Reserved

Synchronize changes

Mirrors the functionality of R0x07 bit 0 (Synchronize changes).

0 = normal operation, update changes to registers that affect image brightness (integration

time, integration delay, gain, horizontal and vertical blank, window size, row/column skip, or row/

column mirror) at the next frame boundary.

1 = do not update any changes to these settings until this bit is returned to ”0.”

CE

Mirrors the functionality of R0x07 bit 1,(Chip Enable).

1 = normal operation.

0 = stop sensor read out. When this is returned to “1,” sensor read out restarts at the starting row

in a new frame.

Chip Version (RO)

22

MT9T031: 1/2-Inch 3-Mp Digital Image Sensor

Name

Sensor Core Register Descriptions

©2006 Aptina Imaging Corporation. All rights reserved.