XC6SLX16-2FTG256C Xilinx Inc, XC6SLX16-2FTG256C Datasheet - Page 16

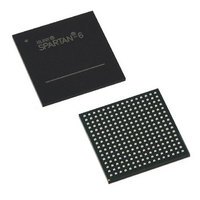

XC6SLX16-2FTG256C

Manufacturer Part Number

XC6SLX16-2FTG256C

Description

FPGA, SPARTAN-6 LX, 14K, 256FTGBGA

Manufacturer

Xilinx Inc

Series

Spartan® 6 LXr

Specifications of XC6SLX16-2FTG256C

No. Of Logic Blocks

2278

No. Of Macrocells

14579

Family Type

Spartan-6

No. Of Speed Grades

2

Total Ram Bits

589824

No. Of I/o's

186

Clock Management

DCM, PLL

I/o Supply Voltage

3.3V

Number Of Logic Elements/cells

14579

Number Of Labs/clbs

1139

Number Of I /o

186

Voltage - Supply

1.14 V ~ 1.26 V

Mounting Type

Surface Mount

Operating Temperature

0°C ~ 85°C

Package / Case

256-LBGA

Package

256FTBGA

Family Name

Spartan®-6

Device Logic Cells

14579

Device Logic Units

9112

Number Of Registers

18224

Typical Operating Supply Voltage

1.2 V

Maximum Number Of User I/os

186

Ram Bits

589824

Core Supply Voltage Range

1.14V

Rohs Compliant

Yes

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Number Of Gates

-

Lead Free Status / RoHS Status

Lead free / RoHS Compliant, Lead free / RoHS Compliant

Other names

122-1672

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

XC6SLX16-2FTG256C

Manufacturer:

TI

Quantity:

21 500

Company:

Part Number:

XC6SLX16-2FTG256C

Manufacturer:

Xilinx Inc

Quantity:

10 000

Table 23: GTP Transceiver Receiver Switching Characteristics

Endpoint Block for PCI Express Designs Switching Characteristics

The Endpoint block for PCI Express is available in the Spartan-6 LXT family. Consult the

Endpoint Block for PCI Express

Table 24: Maximum Performance for PCI Express Designs

DS162 (v2.0) March 31, 2011

Preliminary Product Specification

Notes:

1.

2.

3.

4.

5.

SJ Jitter Tolerance

SJ Jitter Tolerance with Stressed Eye

F

PCIEUSER

Symbol

Using PLL_RXDIVSEL_OUT = 1, 2, and 4.

All jitter values are based on a Bit Error Ratio of 1e

Using 80 MHz sinusoidal jitter only in the absence of deterministic and random jitter.

Composed of 0.37 UI DJ in the form of ISI and 0.18 UI RJ.

Measured using PRBS7 data pattern.

JT_TJSE

JT_SJSE

T

R

JT_TJSE

JT_SJSE

JT_SJ

R

RXELECIDLE

JT_SJ

JT_SJ

JT_SJ

JT_SJ

Symbol

XOOBVDPP

XPPMTOL

R

R

XSST

XRL

3.125

1.62

1.25

614

2.5

3.125

3.125

2.7

2.7

User clock maximum frequency

(2)

Time for RXELECIDLE to respond to loss or restoration of data

OOB detect threshold peak-to-peak

Receiver spread-spectrum tracking

Run length (CID)

Data/REFCLK PPM offset

tolerance

Sinusoidal Jitter

Sinusoidal Jitter

Sinusoidal Jitter

Sinusoidal Jitter

Sinusoidal Jitter

Total Jitter with stressed eye

Sinusoidal Jitter with stressed eye

Total Jitter with stressed eye

Sinusoidal Jitter with stressed eye

for further information.

(2)(5)

Description

(3)

(3)

(3)

(3)

(3)

–12

.

(4)

(4)

Internal AC capacitor bypassed

CDR 2

CDR 2

loop enabled

Description

www.xilinx.com

Spartan-6 FPGA Data Sheet: DC and Switching Characteristics

(1)

nd

nd

-order

-order loop disabled

3.125 Gb/s

Modulated @ 33 KHz

PLL_RXDIVSEL_OUT = 1 –2000

PLL_RXDIVSEL_OUT = 2 –2000

PLL_RXDIVSEL_OUT = 4 –1000

3.125 Gb/s

2.5 Gb/s

1.62 Gb/s

1.25 Gb/s

614 Mb/s

3.125 Gb/s

2.7 Gb/s

2.7 Gb/s

62.5

-3

62.5

-3N

Speed Grade

Spartan-6 FPGA Integrated

–5000

–200

0.65

0.65

Min

0.4

0.4

0.5

0.5

0.5

0.1

0.1

60

–

–

62.5

-2

Typ

75

–

–

–

–

–

–

–

–

–

–

–

–

–

–

–

–

N/A

-1L

2000

2000

1000

Max

150

150

200

–

0

–

–

–

–

–

–

–

–

–

Units

Units

MHz

ppm

ppm

ppm

ppm

ppm

mV

ns

UI

UI

UI

UI

UI

UI

UI

UI

UI

UI

16