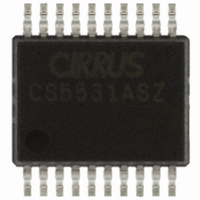

CS5531-ASZ Cirrus Logic Inc, CS5531-ASZ Datasheet - Page 25

CS5531-ASZ

Manufacturer Part Number

CS5531-ASZ

Description

IC ADC 16BIT 2CH W/LNA 20SSOP

Manufacturer

Cirrus Logic Inc

Datasheet

1.CS5531-ASZ.pdf

(50 pages)

Specifications of CS5531-ASZ

Number Of Converters

1

Package / Case

20-SSOP

Number Of Bits

16

Sampling Rate (per Second)

3.84k

Data Interface

Serial

Power Dissipation (max)

45mW

Voltage Supply Source

Analog and Digital, Dual ±

Operating Temperature

-40°C ~ 85°C

Mounting Type

Surface Mount

Number Of Adc Inputs

4

Architecture

Delta-Sigma

Conversion Rate

6.25 SPs to 3840 SPs

Resolution

16 bit

Input Type

Voltage

Interface Type

Serial (3-Wire)

Voltage Reference

2.5 V

Maximum Power Dissipation

500 mW

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

Minimum Operating Temperature

- 40 C

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Lead Free Status / RoHS Status

Lead free / RoHS Compliant, Lead free / RoHS Compliant

Other names

598-1111-5

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

CS5531-ASZ

Manufacturer:

CIRRUS

Quantity:

210

Part Number:

CS5531-ASZ

Manufacturer:

CIRRUS

Quantity:

20 000

from VA+ and VA-. Their output voltage will be

limited to the VA+ voltage for a logic 1 and VA-

for a logic 0.

2.3.7. Offset and Gain Select

The Offset and Gain Select bit (OGS) is used to se-

lect the source of the calibration registers to use

when performing conversions and calibrations.

When the OGS bit is set to ‘0’, the offset and gain

registers corresponding to the desired physical

channel (CS1-CS0 in the selected Setup) will be ac-

cessed. When the OGS bit is set to ‘1’, the offset

and gain registers pointed to by the OG1-OG0 bits

in the selected Setup will be accessed. This feature

allows multiple calibration values (e.g. for different

gain settings) to be used on a single physical chan-

nel without having to re-calibrate or manipulate the

calibration registers.

DS289F5

Figure 9. Input Reference Model when VRS = 1

V

i = fV

n

os

VREF

≤ 8 mV

os

C

VRS = 1; 1 V ≤ V

f =

MCLK

16

φ Coarse

2

φ Fine

C = 14pF

1

REF

≤ 2.5 V

2.3.8. Filter Rate Select

The Filter Rate Select bit (FRS) modifies the output

word rates of the converter to allow either 50 Hz or

60 Hz

4.9152 MHz crystal. If FRS is cleared to logic 0,

the word rates and corresponding filter characteris-

tics can be selected (using the Channel Setup Reg-

isters) from 7.5, 15, 30, 60, 120, 240, 480, 960,

1920, or 3840 Sps when using a 4.9152 MHz clock.

If FRS is set to logic 1, the word rates and corre-

sponding filter characteristics scale by a factor of

5/6, making the selectable word rates 6.25, 12.5,

25, 50, 100, 200, 400, 800, 1600, and 3200 Sps

when using a 4.9152 MHz clock. When using other

clock frequencies, these selectable word rates will

scale linearly with the clock frequency that is used.

Figure 10. Input Reference Model when VRS = 0

V

i = fV

n

os

VREF

≤ 16 mV

rejection

os

C

VRS = 0; 2.5 V < V

f =

CS5531/32/33/34-AS

MCLK

16

when

φ Coarse

2

φ Fine

C = 7 pF

1

operating

REF

≤ VA+

from

25

a