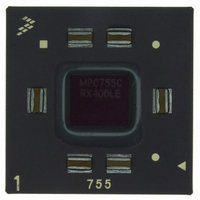

MPC755CRX400LE Freescale Semiconductor, MPC755CRX400LE Datasheet - Page 3

MPC755CRX400LE

Manufacturer Part Number

MPC755CRX400LE

Description

IC MPU 32BIT 400MHZ PPC 360-CBGA

Manufacturer

Freescale Semiconductor

Datasheet

1.MPC755BPX300LE.pdf

(56 pages)

Specifications of MPC755CRX400LE

Processor Type

MPC7xx PowerPC 32-Bit

Speed

400MHz

Voltage

2V

Mounting Type

Surface Mount

Package / Case

360-FCCBGA

Family Name

MPC7xx

Device Core

PowerPC

Device Core Size

64b

Frequency (max)

400MHz

Instruction Set Architecture

RISC

Supply Voltage 1 (typ)

2V

Operating Supply Voltage (max)

2.1V

Operating Supply Voltage (min)

1.9V

Operating Temp Range

0C to 105C

Operating Temperature Classification

Commercial

Mounting

Surface Mount

Pin Count

360

Package Type

FCCBGA

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

Features

-

Lead Free Status / Rohs Status

Not Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

MPC755CRX400LE

Manufacturer:

MOT

Quantity:

12 388

Company:

Part Number:

MPC755CRX400LE

Manufacturer:

Freescale Semiconductor

Quantity:

10 000

2

This section summarizes features of the MPC755 implementation of the PowerPC architecture. Major

features of the MPC755 are as follows:

Freescale Semiconductor

•

•

•

•

•

•

Features

Branch processing unit

— Four instructions fetched per clock

— One branch processed per cycle (plus resolving two speculations)

— Up to one speculative stream in execution, one additional speculative stream in fetch

— 512-entry branch history table (BHT) for dynamic prediction

— 64-entry, four-way set-associative branch target instruction cache (BTIC) for eliminating

Dispatch unit

— Full hardware detection of dependencies (resolved in the execution units)

— Dispatch two instructions to six independent units (system, branch, load/store, fixed-point

— Serialization control (predispatch, postdispatch, execution serialization)

Decode

— Register file access

— Forwarding control

— Partial instruction decode

Completion

— Six-entry completion buffer

— Instruction tracking and peak completion of two instructions per cycle

— Completion of instructions in program order while supporting out-of-order instruction

Fixed point units (FXUs) that share 32 GPRs for integer operands

— Fixed Point Unit 1 (FXU1)—multiply, divide, shift, rotate, arithmetic, logical

— Fixed Point Unit 2 (FXU2)—shift, rotate, arithmetic, logical

— Single-cycle arithmetic, shifts, rotates, logical

— Multiply and divide support (multi-cycle)

— Early out multiply

Floating-point unit and a 32-entry FPR file

— Support for IEEE standard 754 single- and double-precision floating-point arithmetic

— Hardware support for divide

— Hardware support for denormalized numbers

— Single-entry reservation station

— Supports non-IEEE mode for time-critical operations

— Three-cycle latency, one-cycle throughput, single-precision multiply-add

branch delay slots

unit 1, fixed-point unit 2, floating-point)

execution, completion serialization, and all instruction flow changes

MPC755 RISC Microprocessor Hardware Specifications, Rev. 8

Features

3