MC68020RC16E Freescale Semiconductor, MC68020RC16E Datasheet - Page 101

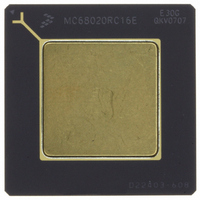

MC68020RC16E

Manufacturer Part Number

MC68020RC16E

Description

IC MPU 32BIT 16MHZ 114-PGA

Manufacturer

Freescale Semiconductor

Datasheet

1.MC68020EH16E.pdf

(306 pages)

Specifications of MC68020RC16E

Processor Type

M680x0 32-Bit

Speed

16MHz

Voltage

5V

Mounting Type

Surface Mount

Package / Case

114-PGA

Family Name

M68000

Device Core

ColdFire

Device Core Size

32b

Frequency (max)

16.67MHz

Instruction Set Architecture

RISC

Supply Voltage 1 (typ)

5V

Operating Supply Voltage (max)

5.25V

Operating Supply Voltage (min)

4.75V

Operating Temp Range

0C to 70C

Operating Temperature Classification

Commercial

Mounting

Through Hole

Pin Count

114

Package Type

CPGA

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Features

-

Lead Free Status / Rohs Status

Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

MC68020RC16E

Manufacturer:

MOT

Quantity:

900

Company:

Part Number:

MC68020RC16E

Manufacturer:

MOT

Quantity:

900

Part Number:

MC68020RC16E

Manufacturer:

MOTOROLA/摩托罗拉

Quantity:

20 000

- Current page: 101 of 306

- Download datasheet (3Mb)

The acceptable bus cycle terminations for asynchronous cycles are summarized in

relation to DSACK1/DSACK0 assertion as follows (case numbers refer to Table 5-8):

Normal Termination:

Halt Termination:

Bus Error Termination:

Retry Termination:

Legend:

5-54

Case No.

DSACK1/DSACK0 is asserted; BERR and HALT remain negated (case 1).

HALT is asserted at same time or before DSACK1/DSACK0, and BERR remains

negated (case 2).

BERR is asserted in lieu of, at the same time, or before DSACK1/DSACK0 (case 3) or

after DSACK1/DSACK0 (case 4), and HALT remains negated; BERR is negated at the

same time or after DSACK1/DSACK0.

HALT and BERR are asserted in lieu of, at the same time, or before DSACK1/DSACK0

(case 5) or after DSACK1/DSACK0 (case 6); BERR is negated at the same time or after

DSACK1/DSACK0; HALT may be negated at the same time or after BERR.

n—The number of current even bus state (e.g., S2, S4, etc.)

A—Signal is asserted in this bus state

N—Signal is not asserted and/or remains negated in this bus state

X—Don’t care

S—Signal was asserted in previous state and remains asserted in this state

1

2

3

4

5

6

DSACK1/DSACK0

DSACK1/DSACK0

DSACK1/DSACK0

DSACK1/DSACK0

DSACK1/DSACK0

DSACK1/DSACK0

Table 5-8.

Control Signal

BERR

BERR

BERR

BERR

BERR

BERR

HALT

HALT

HALT

HALT

HALT

HALT

DSACK1/DSACK0

Freescale Semiconductor, Inc.

For More Information On This Product,

Asserted on Rising

A/S

N/A

N/A

A/S

A

N

N

A

N

A

N

A

N

N

A

A

N

N

n

Edge of State

M68020 USER’S MANUAL

Go to: www.freescale.com

n+2

,

S

N

X

S

N

S

X

S

N

X

A

N

X

S

S

X

A

A

BERR

Normal cycle terminate and continue.

Normal cycle terminate and halt. Continue when

HALT negated.

Terminate and take bus error exception, possibly

deferred.

Terminate and take bus error exception, possibly

deferred.

Terminate and retry when HALT negated.

Terminate and retry when HALT negated.

,

HALT

Assertion Results

Result

MOTOROLA

Related parts for MC68020RC16E

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

(MC600 Series) INTEGRATED CIRCUITS

Manufacturer:

ETC

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet: