MC68020RC16E Freescale Semiconductor, MC68020RC16E Datasheet - Page 165

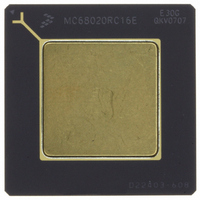

MC68020RC16E

Manufacturer Part Number

MC68020RC16E

Description

IC MPU 32BIT 16MHZ 114-PGA

Manufacturer

Freescale Semiconductor

Datasheet

1.MC68020EH16E.pdf

(306 pages)

Specifications of MC68020RC16E

Processor Type

M680x0 32-Bit

Speed

16MHz

Voltage

5V

Mounting Type

Surface Mount

Package / Case

114-PGA

Family Name

M68000

Device Core

ColdFire

Device Core Size

32b

Frequency (max)

16.67MHz

Instruction Set Architecture

RISC

Supply Voltage 1 (typ)

5V

Operating Supply Voltage (max)

5.25V

Operating Supply Voltage (min)

4.75V

Operating Temp Range

0C to 70C

Operating Temperature Classification

Commercial

Mounting

Through Hole

Pin Count

114

Package Type

CPGA

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Features

-

Lead Free Status / Rohs Status

Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

MC68020RC16E

Manufacturer:

MOT

Quantity:

900

Company:

Part Number:

MC68020RC16E

Manufacturer:

MOT

Quantity:

900

Part Number:

MC68020RC16E

Manufacturer:

MOTOROLA/摩托罗拉

Quantity:

20 000

- Current page: 165 of 306

- Download datasheet (3Mb)

7.2.2.1 BRANCH ON COPROCESSOR CONDITION INSTRUCTION. The conditional

instruction category includes two formats of the M68000 family branch instruction. These

instructions branch on conditions related to the coprocessor operation. They execute

similarly to the conditional branch instructions provided in the M68000 family instruction

set.

7.2.2.1.1 Format. Figure 7-9 shows the format of the branch on coprocessor condition

instruction that provides a word-length displacement. Figure 7-10 shows the format of this

instruction that includes a long-word displacement.

The first word of the branch on coprocessor condition instruction is the F-line operation

word. Bits 15–12 = 1111 and bits 11–9 contain the CpID code of the coprocessor that is to

evaluate the condition. The value in bits 8–6 identifies either the word or the long-word

displacement format of the branch instruction, which is specified by the cpBcc.W or

cpBcc.L mnemonic, respectively. Bits 5–0 of the F-line operation word contain the

coprocessor condition selector field. The MC68020/EC020 writes the entire operation

word to the condition CIR to initiate execution of the branch instruction by the

coprocessor. The coprocessor uses bits 5–0 to determine which condition to evaluate.

If the coprocessor requires additional information to evaluate the condition, the branch

instruction format can include this information in extension words. Following the F-line

operation word, the number of extension words is determined by the coprocessor design.

The final word(s) of the cpBcc instruction format contains the displacement used by the

main processor to calculate the destination address when the branch is taken.

7.2.2.1.2 Protocol. Figure 7-8 shows the protocol for the cpBcc.L and cpBcc.W

instructions. The main processor initiates the instruction by writing the F-line operation

word to the condition CIR to transfer the condition selector to the coprocessor. The main

7-12

15

15

1

1

14

14

1

1

13

13

1

1

Figure 7-10. Branch on Coprocessor Condition

Figure 7-9. Branch on Coprocessor Condition

12

12

1

1

Freescale Semiconductor, Inc.

For More Information On This Product,

OPTIONAL COPROCESSOR-DEFINED EXTENSION WORDS

OPTIONAL COPROCESSOR-DEFINED EXTENSION WORDS

11

11

Instruction Format (cpBcc.W)

Instruction Format (cpBcc.L)

CpID

CpID

M68020 USER’S MANUAL

Go to: www.freescale.com

DISPLACEMENT — HIGH

9

9

DISPLACEMENT — LOW

DISPLACEMENT

0

0

8

8

1

1

7

7

6

0

6

1

5

5

CONDITION SELECTOR

CONDITION SELECTOR

MOTOROLA

0

0

Related parts for MC68020RC16E

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

(MC600 Series) INTEGRATED CIRCUITS

Manufacturer:

ETC

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet: