CYV15G0204RB-BGC Cypress Semiconductor Corp, CYV15G0204RB-BGC Datasheet - Page 18

CYV15G0204RB-BGC

Manufacturer Part Number

CYV15G0204RB-BGC

Description

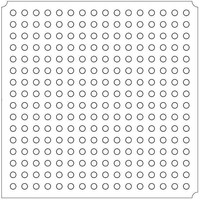

IC DESERIAL HOTLINK 256LBGA

Manufacturer

Cypress Semiconductor Corp

Type

Deserializerr

Datasheet

1.CYV15G0204RB-BGXC.pdf

(24 pages)

Specifications of CYV15G0204RB-BGC

Package / Case

256-LBGA Exposed Pad, 32-HLBGA

Function

Deserializer

Data Rate

1.485Gbps

Input Type

PECL

Output Type

LVTTL

Number Of Inputs

2

Number Of Outputs

2

Voltage - Supply

3.15 V ~ 3.45 V

Operating Temperature

0°C ~ 70°C

Mounting Type

Surface Mount

Operating Supply Voltage

3.3 V

Supply Current

700 mA

Maximum Operating Temperature

+ 70 C

Minimum Operating Temperature

0 C

Mounting Style

SMD/SMT

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

CYV15G0204RB-BGC

Manufacturer:

Cypress Semiconductor Corp

Quantity:

10 000

Document #: 38-02103 Rev. *C

CYV15G0204RB AC Electrical Characteristics

CYV15G0204RB Receiver LVTTL Switching Characteristics Over the Operating Range

f

t

t

t

t

t

t

f

t

t

CYV15G0204RB TRGCLKx Switching Characteristics Over the Operating Range

f

t

t

t

t

t

t

t

CYV15G0204RB Bus Configuration Write Timing Characteristics Over the Operating Range

t

t

t

CYV15G0204RB JTAG Test Clock Characteristics Over the Operating Range

f

t

CYV15G0204RB Device RESET Characteristics Over the Operating Range

t

Notes

RS

RXCLKP

RXCLKD

RXCLKR

RXCLKF

RXDv–

RXDv+

ROS

RECLKO

RECLKOD

TRG

TRGCLK

TRGH

TRGL

TRGD

TRGR

TRGF

TRGRX

DATAH

DATAS

WRENP

TCLK

TCLK

RST

14. Tested initially and after any design or process changes that may affect these parameters, but not 100% tested.

15. The ratio of rise time to falling time must not vary by greater than 2:1.

16. For a given operating frequency, neither rise or fall specification can be greater than 20% of the clock-cycle period or the data sheet maximum time.

17. All transmit AC timing parameters measured with 1ns typical rise time and fall time.

18. Parallel data output specifications are only valid if all outputs are loaded with similar DC and AC loads.

19. Receiver UI (Unit Interval) is calculated as 1/(f

20. The duty cycle specification is a simultaneous condition with the t

21. TRGCLKx± has no phase or frequency relationship with the recovered clock(s) and only acts as a centering reference to reduce clock synchronization time.

Parameter

cycle cannot be as large as 30%–70%.

TRGCLKx± must be within ±1500 PPM (±0.15%) of the transmitter PLL reference (REFCLKx±) frequency. Although transmitting to a HOTLink II receiver channel

necessitates the frequency difference between the transmitter and receiver reference clocks to be within ±1500-PPM, the stability of the crystal needs to be

within the limits specified by the appropriate standard when transmitting to a remote receiver that is compliant to that standard.

[14, 15, 16, 17]

[20]

[14, 15, 16, 17]

[18]

[18]

[21]

[14]

[14]

RXCLKx± Clock Output Frequency

RXCLKx± Period = 1/f

RXCLKx± Duty Cycle Centered at 50% (Full Rate and Half Rate)

RXCLKx± Rise Time

RXCLKx± Fall Time

Status and Data Valid Time to RXCLKx± (RXRATEx = 0) (Full Rate)

Status and Data Valid Time to RXCLKx± (RXRATEx = 1) (Half Rate)

Status and Data Valid Time to RXCLKx± (RXRATEx = 0) (Full Rate)

Status and Data Valid Time to RXCLKx± (RXRATEx = 1) (Half Rate)

RECLKOx Clock Frequency

RECLKOx Period=1/f

RECLKOx Duty Cycle centered at 60% HIGH time

TRGCLKx Clock Frequency

TRGCLKx Period = 1/f

TRGCLKx HIGH Time (TRGRATEx = 1)(Half Rate)

TRGCLKx HIGH Time (TRGRATEx = 0)(Full Rate)

TRGCLKx LOW Time (TRGRATEx = 1)(Half Rate)

TRGCLKx LOW Time (TRGRATEx = 0)(Full Rate)

TRGCLKx Duty Cycle

TRGCLKx Rise Time (20%–80%)

TRGCLKx Fall Time (20%–80%)

TRGCLKx Frequency Referenced to Received Clock Frequency

Bus Configuration Data Hold

Bus Configuration Data Setup

Bus Configuration WREN Pulse Width

JTAG Test Clock Frequency

JTAG Test Clock Period

Device RESET Pulse Width

TRG

ROS

RS

* 20) (when TRGRATEx = 1) or 1/(f

REF

Description

REFH

and t

REFL

TRG

parameters. This means that at faster character rates the TRGCLKx± duty

* 10) (when TRGRATEx = 0). In an operating link this is equivalent to t

5UI–2.0

5UI–1.3

5UI–1.8

5UI–2.6

2.9

2.9

–0.15

Min.

9.75

6.66

–1.0

19.5

6.66

–1.9

19.5

0.3

0.3

6.6

5.9

5.9

30

10

10

50

30

0

CYV15G0204RB

[14]

[14]

[19]

[19]

[19]

[19]

102.56

51.28

51.28

+0.15

Max

+1.0

150

150

150

1.2

1.2

70

20

0

2

2

Page 18 of 24

MHz

MHz

MHz

MHz

Unit

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

B

%

%

.

[+] Feedback