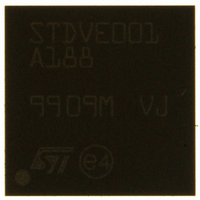

STDVE001AQTR STMicroelectronics, STDVE001AQTR Datasheet

STDVE001AQTR

Specifications of STDVE001AQTR

Available stocks

Related parts for STDVE001AQTR

STDVE001AQTR Summary of contents

Page 1

... Equalizer regenerates the incoming attenuated TMDS signal Table 1. Device summary Order code Operating temperature STDVE001ABTR STDVE001AQTR 6 December 2010 ■ Buffer drives the TMDS outputs over long PCB track lengths ■ Low output skew and jitter ■ Tight input thresholds reduce bit error rates On-chip selectable 50 Ω ...

Page 2

Contents Contents 1 Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ...

Page 3

STDVE001A 9 Package mechanical data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ...

Page 4

Contents List of tables Table 1. Device summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ...

Page 5

STDVE001A List of figures Figure 1. STDVE001A block diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ...

Page 6

Description 1 Description The STDVE001A integrates a 4-channel 3.4 Gbps TMDS equalizer. High-speed data paths and flow-through pinout minimize the internal device jitter and simplify the board layout. The equalizer overcomes the intersymbol interference (ISI) jitter effects from lossy cables. ...

Page 7

STDVE001A 2 Block diagram Figure 1. STDVE001A block diagram Doc ID 14855 Rev 4 Block diagram 7/48 ...

Page 8

Block diagram Figure 2. Equalizer functional diagram (one signal pair) Figure 3. DDC I 8/ bus repeater Doc ID 14855 Rev 4 STDVE001A ...

Page 9

STDVE001A 3 Application diagram Figure 4. STDVE001A in a digital TV Doc ID 14855 Rev 4 Application diagram 9/48 ...

Page 10

Pin configuration 4 Pin configuration Figure 5. Pin configuration (TQFP48 package) 10/48 Doc ID 14855 Rev 4 STDVE001A ...

Page 11

STDVE001A Figure 6. Pin configuration (QFN48 package) Doc ID 14855 Rev 4 Pin configuration 11/48 ...

Page 12

Pin configuration Table 2. Pin description Pin Pin name Type number 1 GND Power Ground 2 VCC Power 3.3 V ± supply 3 CEC_IO I/O 4 CEC_IO_INT I/O 5 GND Power Ground 6 REXT Analog 7 HPD_EXT Output ...

Page 13

STDVE001A Table 2. Pin description (continued) Pin Pin name Type number 25 OE_N Input 26 VDD_INT Power DC supply for DDC, HPD and CEC (can 3 unconnected). 27 GND Power Ground 28 SCL_INT I/O ...

Page 14

Functional description 5 Functional description The STDVE001A routes physical layer signals for high bandwidth digital video and is compatible with low voltage differential signaling standard like TMDS. The device passes the differential inputs from a video source to a common ...

Page 15

STDVE001A Figure 7. STDVE001A gain vs. frequency The equalizer of STDVE001A is fully adaptive and automatic in function. The default setting recommended for optimal operation. The equalizer performance is optimized for all frequencies over the ...

Page 16

Functional description TMDS voltage levels The TMDS interface standard is a signaling method intended for point-to-point communication over a tightly controlled impedance medium. The TMDS standard uses a lower voltage swing than other common communication standards, achieving higher data rates ...

Page 17

STDVE001A STDVE001A buffers both the serial data (DDC SDA) and serial clock (DDC SCL) on the I bus, while retaining all the operating modes and features of the I two buses of 400 pF bus capacitance to be connected in ...

Page 18

Functional description The output voltage swing depends on 3 components: supply voltage (V resistor (R ) and current drive (I T termination resistor can vary from 50 The voltage on the output is given by ...

Page 19

STDVE001A 6 Maximum ratings Stressing the device above the rating listed in device. These are stress ratings only and operation of the device at these or any other conditions above those indicated in the operating sections of this specification is ...

Page 20

DC and AC characteristics 7 DC and AC characteristics 7.1 DC electrical characteristics T = -40 to +85 ° Table 8. Power supply characteristics Symbol Parameter V Supply voltage CC I Supply current CC Table 9. DC specifications ...

Page 21

STDVE001A Table 10. DC specifications for TMDS differential outputs Symbol Parameter Single-ended high level V OH output voltage Single-ended low level V OL output voltage Single ended output V swing swing voltage Differential output V voltage OD (1) (peak-to-peak) Differential ...

Page 22

DC and AC characteristics Table 11. DC specifications for OE_N, EQ_BOOST, EQ_BOOST2, PRE, DDC_EN inputs Symbol Parameter V HIGH level input voltage IH V LOW level input voltage IL V Clamp diode voltage IK I Input high current IH I ...

Page 23

STDVE001A Table 14. DDC I/O pins Symbol Parameter V Input voltage I(DDC) I Input leakage current I(leak) C Input/output capacitance I/O Table 15. Status pins (HPD_INT) Symbol Parameter V High level input voltage IH V Low level input voltage IL ...

Page 24

DC and AC characteristics HPD_EXT) Table 16. Status pins ( Symbol Parameter V Voltage C Input/output capacitance I/O Output low voltage V OL (open-drain I/Os) 1. Typical parameters are measured at V 24/48 (1) Test condition ...

Page 25

STDVE001A 7.2 DC electrical characteristics ( -40 to +85 ° Table 17. Supplies Symbol Parameter V DC supply voltage CC Table 18. Input/output SDA, SCL Symbol Parameter High level input V IH voltage Low level input ...

Page 26

DC and AC characteristics 7.3 DC electrical characteristics (CEC -40 to +85 ° Table 19. DC electrical characteristics (CEC) Symbol V DC supply voltage CC V Logic 0 output OL V Logic 1 output OH High ...

Page 27

STDVE001A 7.4 Dynamic switching characteristics (T = -40 to +85 ° Typical values are at T Table 20. Clock and data rate Symbol Parameter Clock frequency f (1/ the CK differential data rate) D Signaling rate ...

Page 28

DC and AC characteristics Table 23. Turn-on and turn-off times Symbol Parameter TMDS output enable t ON time TMDS output disable t OFF time Table 24. Status pins (HPD_INT, HPD_EXT, OE_N Symbol Parameter Propagation delay t (from Y_HPD to the ...

Page 29

STDVE001A 7.5 Dynamic switching characteristics ( -40 to +85 ° Typical values are (1) Table 26 repeater Symbol Parameter clock frequency SCL t Low duration on ...

Page 30

DC and AC characteristics 2 (1) Table 26 repeater (continued) Symbol Parameter High duration on SCL t HIGH pin t Propagation delay PHL t Propagation delay PLH t Propagation delay PHL t Propagation delay PLH t Propagation delay ...

Page 31

STDVE001A 2 (1) Table 26 repeater (continued) Symbol Parameter t Output fall time f t Output fall time f t Output rise time r t Output rise time r 1. All the timing values are tested during characterization ...

Page 32

DC and AC characteristics Figure 8. Test circuit for electrical characteristics load capacitance: include jig and probe capacitance termination resistance; should be equal Figure 9. TMDS output driver 1. Z ...

Page 33

STDVE001A Figure 10. Test circuit for HDMI receiver and driver = 50 Ω Figure 11. Test circuit for turn-on and turn-off times pF. L Doc ID 14855 Rev 4 DC and AC ...

Page 34

DC and AC characteristics Figure 12. Test circuit for short-circuit output current Figure 13. Propagation delays 34/48 Doc ID 14855 Rev 4 STDVE001A ...

Page 35

STDVE001A Figure 14. Turn-on and turn-off times Doc ID 14855 Rev 4 DC and AC characteristics 35/48 ...

Page 36

DC and AC characteristics Figure 15. t SK(O) Figure 16. t SK(P) 36/48 Doc ID 14855 Rev 4 STDVE001A ...

Page 37

STDVE001A Figure 17. t SK(D) Figure 18. AC waveform 1 (I Figure 19. Test circuit for AC measurements (I = load resistor; 1.35 kΩ load capacitance includes jig and probe capacitance; 7 pF. ...

Page 38

DC and AC characteristics 2 Figure 20 bus timing 38/48 Doc ID 14855 Rev 4 STDVE001A ...

Page 39

STDVE001A 8 Application information 8.1 Power supply sequencing Proper power-supply sequencing is advised for all CMOS devices recommended to always apply V CC 8.2 Power supply requirements Bypass each of the V device as possible, with the smaller-valued ...

Page 40

Application information Figure 21. Typical application of I The STDVE001A DDC lines are 5 V tolerant does not require any extra circuitry to translate between the different bus voltages. 40/ bus system Doc ID 14855 Rev ...

Page 41

STDVE001A 9 Package mechanical data In order to meet environmental requirements, ST offers these devices in different grades of ® ECOPACK packages, depending on their level of environmental compliance. ECOPACK specifications, grade definitions and product status are available at: www.st.com. ...

Page 42

Package mechanical data Table 28. TQFP48 ( mm) mechanical data Symbol ccc / ddd 42/48 Millimeters Min Typ − 0.05 0.10 0.95 1.00 ...

Page 43

STDVE001A Figure 23. TQFP48 ( mm) footprint recommendation Doc ID 14855 Rev 4 Package mechanical data 43/48 ...

Page 44

Package mechanical data Figure 24. TQFP48 ( mm) tape and reel information 44/48 Doc ID 14855 Rev 4 STDVE001A ...

Page 45

STDVE001A Figure 25. QFN48 ( mm) package outline Doc ID 14855 Rev 4 Package mechanical data 45/48 ...

Page 46

Package mechanical data Table 29. QFN48 ( mm) package mechanical data Symbol ddd 46/48 Millimeters Min Typ 0.80 0.90 − 0.02 − 0.65 − 0.25 0.18 0.23 ...

Page 47

STDVE001A 10 Revision history Table 30. Document revision history Date 02-Jul-2008 21-Jul-2008 28-Jul-2009 06-Dec-2010 Revision 1 Initial release. Modified: Figure 2 and 2 Replaced ‘equation’ with ‘equalizer in the Features section. Document status promoted from preliminary data to datasheet. 3 ...

Page 48

... Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries (“ST”) reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any time, without notice. All ST products are sold pursuant to ST’s terms and conditions of sale. ...