STDVE001AQTR STMicroelectronics, STDVE001AQTR Datasheet - Page 39

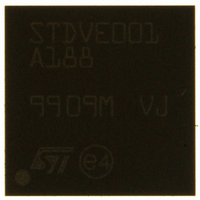

STDVE001AQTR

Manufacturer Part Number

STDVE001AQTR

Description

IC EQUALIZER TMDS/HDMI 48-QFN

Manufacturer

STMicroelectronics

Datasheet

1.STDVE001AQTR.pdf

(48 pages)

Specifications of STDVE001AQTR

Applications

TV

Interface

I²C

Voltage - Supply

3.135 V ~ 3.465 V

Package / Case

48-QFN

Mounting Type

Surface Mount

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Other names

497-8383-2

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

STDVE001AQTR

Manufacturer:

STMicroelectronics

Quantity:

1 000

STDVE001A

8

8.1

8.2

8.3

8.4

Application information

Power supply sequencing

Proper power-supply sequencing is advised for all CMOS devices. It is recommended to

always apply V

Power supply requirements

Bypass each of the V

device as possible, with the smaller-valued capacitor as close to the V

possible.

All V

from each V

variation can only be ± 5% as per the HDMI specifications.

The maximum tolerable noise ripple on 3.3 V supply must be within a specified limit.

Differential traces

The high-speed TMDS inputs are the most critical parts for the device. There are several

considerations to minimize discontinuities on these transmission lines between the

connectors and the device.

Output trace characteristics affect the performance of the STDVE001A. Use controlled

impedance traces to match trace impedance to both the transmission medium impedance

and termination resistor. Run the differential traces close together to minimize the effects of

the noise. Reduce skew by matching the electrical length of the traces. Avoid discontinuities

in the differential trace layout. Avoid 90 degree turns and minimize the number of vias to

further prevent impedance discontinuities.

I

A typical application is shown in the figure below. In the example, the system master is

running on a 3.3 V I

100 kHz unless the slave bus is isolated and then the master bus can run at 400 kHz.

Master devices can be placed on either bus.

2

C lines application information

CC

a)

b)

c)

d)

pins can be tied to a single 3.3 V power source. A 0.01 μF capacitor is connected

Maintain 100-Ω differential transmission line impedance into and out of the

STDVE001A.

Keep an uninterrupted ground plane below the high-speed I/Os.

Keep the ground-path vias to the device as close as possible to allow the shortest

return current path.

Layout of the TMDS differential inputs should be with the shortest stubs from the

connectors.

CC

CC

pin directly to ground to filter supply noise. The maximum power supply

before applying any signals to the input/output or control pins.

2

C-bus while the slave is connected to a 5 V bus. Both buses run at

CC

pins with 0.1 μF and 1 nF capacitors in parallel as close to the

Doc ID 14855 Rev 4

Application information

CC

pin of the device as

39/48