STDVE001AQTR STMicroelectronics, STDVE001AQTR Datasheet - Page 16

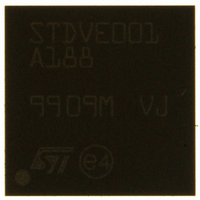

STDVE001AQTR

Manufacturer Part Number

STDVE001AQTR

Description

IC EQUALIZER TMDS/HDMI 48-QFN

Manufacturer

STMicroelectronics

Datasheet

1.STDVE001AQTR.pdf

(48 pages)

Specifications of STDVE001AQTR

Applications

TV

Interface

I²C

Voltage - Supply

3.135 V ~ 3.465 V

Package / Case

48-QFN

Mounting Type

Surface Mount

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Other names

497-8383-2

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

STDVE001AQTR

Manufacturer:

STMicroelectronics

Quantity:

1 000

Functional description

5.2

5.3

5.4

5.5

16/48

TMDS voltage levels

The TMDS interface standard is a signaling method intended for point-to-point

communication over a tightly controlled impedance medium. The TMDS standard uses

a lower voltage swing than other common communication standards, achieving higher data

rates with reduced power consumption while reducing EMI emissions and system

susceptibility to noise. The device is capable of detecting differential signals as low as

100 mV within the entire common mode voltage range.

Operating modes

Table 4.

The OE_N input activates a hardware power down mode. When the power down mode is

active (OE_N = H), all input and output buffers and internal bias circuitry are powered-off

and disabled.

Outputs are tri-stated in power-down mode. When exiting power-down mode, there is

a delay associated with turning on band-references and input/output buffer circuits.

Note that the OE_N pin is only used to disable the TMDS paths in the chip to same

maximum amount of current. It does not affect the HPD, DDC and CEC portions. The DDC

is controlled only by the DDC_EN pin whereas the HPD and CEC are always active as long

as the supply to the chip is present.

HPD pins

The input pin HPD_INT is 5 V tolerant, allowing direct connection to 5 V signals. The output

HPD pin has open-drain structure so that the disabled HPD output is driven to GND

whereas the enabled HPD port has the same polarity as the HPD_INT. Note that the HPD

output should have an external pull-up resistor connected to +5 V from the HDMI source.

DDC channels

The DDC channels are designed together with a bi-directional buffer so as to ensure the

voltage levels on the I

eliminates the errors during EDID and HDCP reading.

I

The device contains two identical bi-directional open-drain, non-inverting buffer circuits that

enable I

2

OE_N

C DDC line repeater

H

L

L

2

C DDC bus lines to be extended without degradation in system performance. The

OE_N operating modes

IN+

H

X

L

2

C lines are met even after long capacitive cables. This feature

Input

Doc ID 14855 Rev 4

IN-

H

L

X

OUT+

Hi-Z

H

L

Output

OUT-

Hi-Z

H

L

Low power mode

Active mode

Active mode

Function

STDVE001A