MC68HC11K Motorola, MC68HC11K Datasheet

MC68HC11K

Available stocks

Related parts for MC68HC11K

MC68HC11K Summary of contents

Page 1

... The M68HC11 K-series microcontroller units (MCUs) are high-performance derivatives of the MC68HC11F1 and have several additional features. The MC68HC11K0, MC68HC11K1, MC68HC11K3, MC68HC11K4 and MC68HC711K4 comprise the series. These MCUs, with a nonmul- tiplexed expanded bus, are characterized by high speed and low power consumption. Their fully static design allows operation at frequencies from 4 MHz to dc ...

Page 2

... MC68HC711K4CFN4 2 MHz MC68HC711K4VFN2 3 MHz MC68HC711K4VFN3 4 MHz MC68HC711K4VFN4 2 MHz MC68HC711K4MFN2 3 MHz MC68HC711K4MFN3 4 MHz MC68HC711K4MFN4 4 MHz MC68HC11K4BCFU4 2 MHz MC68HC11K1CFU2 3 MHz MC68HC11K1CFU3 4 MHz MC68HC11K1CFU4 2 MHz MC68HC11K1VFU2 3 MHz MC68HC11K1VFU3 4 MHz MC68HC11K1VFU4 2 MHz MC68HC11K0CFU2 3 MHz MC68HC11K0CFU3 4 MHz MC68HC11K0CFU4 2 MHz MC68HC11K0VFU2 3 MHz MC68HC11K0VFU3 4 MHz MC68HC11K0VFU4 M68HC11 K Series ...

Page 3

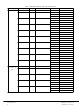

... CLCC – (Windowed) – 105 C – 125 C Table 2 Extended Voltage (3.0 Vdc to 5.5 Vdc) Device Ordering Information Package Temperature 84-Pin PLCC – 80-Pin QFP – M68HC11 K Series MC68HC11KTS/D CONFIG Description $DF EPROM $DF EPROM $DF EPROM Description Frequency Custom ROM 1 MHz 3 MHz ...

Page 4

... Custom ROM, No EEPROM 2 MHz 3 MHz 4 MHz MC Order Number MC68HC11K4CFN2 MC68HC11K4CFN3 MC68HC11K4CFN4 MC68HC11K4VFN2 MC68HC11K4VFN3 MC68HC11K4VFN4 MC68HC11K4MFN2 MC68HC11K4MFN3 MC68HC11K4MFN4 MC68HC11K3CFN2 MC68HC11K3CFN3 MC68HC11K3CFN4 MC68HC11K3VFN2 MC68HC11K3VFN3 MC68HC11K3VFN4 MC68HC11K3MFN2 MC68HC11K3MFN3 MC68HC11K3MFN4 MC68HC11K4CFU2 MC68HC11K4CFU3 MC68HC11K4CFU4 MC68HC11K4VFU2 MC68HC11K4VFU3 MC68HC11K4VFU4 MC68HC11K3CFU2 MC68HC11K3CFU3 MC68HC11K3CFU4 MC68HC11K3VFU2 MC68HC11K3VFU3 MC68HC11K3VFU4 M68HC11 K Series MC68HC11KTS/D ...

Page 5

... PG2/XA15 31 PG1/XA14 32 1. Pins 20, 22, and 25 are used only during factory testing and should not be connected to external circuitry PPE applies only to devices with EPROM. Figure 1 Pin Assignments for 84-Pin PLCC/CLCC M68HC11 K Series MC68HC11KTS/D 1 MC68HC11K SERIES 74 PD2/MISO 73 PD1/TxD 72 PD0/RxD 71 MODA/LIR 70 MODB/V STBY ...

Page 6

... PA3/OC5/IC4/OC1 8 PA2/IC1 9 PA1/IC2 10 PA0/IC3 PB7/ADDR15 14 PB6/ADDR14 15 PB5/ADDR13 16 PB4/ADDR12 17 PB3/ADDR11 18 PB2/ADDR10 19 PB1/ADDR9 20 Figure 2 Pin Assignments for 80-Pin TQFP MOTOROLA 6 MC68HC11K SERIES 60 PF0/ADDR0 59 PF1/ADDR1 58 PF2/ADDR2 57 PF3/ADDR3 56 PF4/ADDR4 55 PF5/ADDR5 54 PF6/ADDR6 53 PF7/ADDR7 PE0/AN0 48 PE1/AN1 47 PE2/AN2 ...

Page 7

... PC5 DATA5 PC4 DATA4 PC3 DATA3 PC2 DATA2 PC1 DATA1 PC0 DATA0 R/W * XOUT pin omitted on 80-pin QFP. Figure 3 M68HC11 K-Series Block Diagram M68HC11 K Series MC68HC11KTS/D OSCILLATOR CLOCK MODE CONTROL LOGIC COP TIMER SYSTEM PERIODIC INTERRUPT 24 KBYTES 640 ROM/ BYTES EPROM EEPROM ...

Page 8

... Examples of Memory Expansion Using Chip Selects .....................................................35 5 Resets and Interrupts 6 Parallel Input/Output 7 Serial Communications Interface 8 Serial Peripheral Interface 9 Analog-to-Digital Converter 10 Main Timer 10.1 Real-Time Interrupt ...................................................................................................................70 11 Pulse Accumulator 12 Pulse-Width Modulation Timer 12.1 PWM Boundary Cases ..............................................................................................................78 MOTOROLA 8 TABLE OF CONTENTS Page M68HC11 K Series MC68HC11KTS/D ...

Page 9

... PORTC Port C Data PORTE Port E Data PORTF Port F Data PORTG Port G Data PORTH Port H Data PPAR Port Pull-Up Assignment PPROG EEPROM Programming Control PWCLK Pulse-Width Modulation Clock Select M68HC11 K Series MC68HC11KTS/D REGISTER INDEX $000B 66 $003F 25 $003A 40 $005A ...

Page 10

... S $0070, $0071 $0072 $0073 $0074 $0075 $0028 $0028 $002A $0029 T $000E, $000F $0021 $0025 $001E–$001F $0022 $0024 $0016–$001D 62 M68HC11 K Series MC68HC11KTS/D ...

Page 11

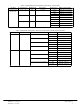

... HPRIO —Highest Priority I-Bit Interrupt and Miscellaneous Bit RBOOT* SMOD* MDA* RESET *The reset values of RBOOT, SMOD, and MDA depend on the mode selected at power up. M68HC11 K Series MC68HC11KTS PSEL4 PSEL3 PSEL2 PSEL1 PSEL0 ...

Page 12

... E Clock Out IRV Out of of Reset Reset On Off On Off On Off On On Latched at Reset SMOD MDA $0038 1 Bit 0 XDV1 XDV0 0 0 IRVNE IRVNE Can Affects Only Be Written E Once IRV Once E Anytime IRV Anytime M68HC11 K Series MC68HC11KTS/D ...

Page 13

... XDV[1:0] —XOUT Clock Divide Select Controls the frequency of the clock driven out of the XOUT pin XDV XOUT = EXTAL [1:0] Divided M68HC11 K Series MC68HC11KTS/D Frequency at Frequency at EXTAL = 8 MHz EXTAL = 12 MHz 8 MHz 12 MHz 2 MHz 3 MHz 1.3 MHz 2 MHz 1 MHz 1.5 MHz Frequency at EXTAL = 16 MHz ...

Page 14

... EXT $A000 $FFFF SINGLE EXPANDED BOOTSTRAP CHIP NOTE: ROM/EPROM can be enabled in special test mode by setting ROMON bit in the config register after reset. MOTOROLA 14 128-BYTE REGISTER BLOCK x000 (CAN BE REMAPPED TO ANY x07F 4K PAGE BY THE INIT REGISTER) x080 EXT 768 BYTES RAM ...

Page 15

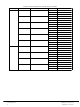

... PORTC DDC1 DDC0 DDRC PD1 PD0 PORTD DDD1 DDD0 DDRD PE1 PE0 PORTE 0 0 CFORC 0 0 OC1M 0 0 OC1D 9 Bit 8 TCNT (High) 1 Bit 0 TCNT (Low) 9 Bit 8 TIC1 (High) 1 Bit 0 TIC1 (Low) 9 Bit 8 TIC2 (High) 1 Bit 0 TIC2 (Low) 9 Bit 8 TIC3 (High) MOTOROLA 15 ...

Page 16

... EVEN LVPI $003C RBOOT SMOD MDA $003D RAM3 RAM2 RAM1 $003E TILOP 0 OCCR $003F ROMAD 1 CLKX $0040 to $0055 $0056 MXGS2 MXGS1 W2SZ1 $0057 W2A15 W2A14 W2A13 MOTOROLA ...

Page 17

... Bit 0 PWDTY1 1 Bit 0 PWDTY2 1 Bit 0 PWDTY3 1 Bit 0 PWDTY4 SBR9 SBR8 SCBDH SBR1 SBR0 SCBDL PE PT SCCR1 RWU SBK SCCR2 FE PF SCSR1 0 RAF SCSR2 0 0 SCDRH R1/T1 R0/T0 SCDRL Reserved Reserved PH1 PH0 PORTH DDH1 DDH0 DDRH PG1 PG0 PORTG DDG1 DDG0 DDRG MOTOROLA 17 ...

Page 18

... Standard devices have 24 kbytes of EPROM (OTPROM in a non-windowed package). Custom ROM devices have a 24-Kbyte ROM array that is mask programmed at the factory to customer specifications. The MC68HC11K0, MC68HC11K1, MC68L11K0, and MC68L11K1 have no ROM/EPROM. Refer to the ordering information tables. The ROMAD and ROMON control bits in the CONFIG register control the position and presence of ROM/EPROM in the memory map. The ROM/EPROM can be mapped at $2000– ...

Page 19

... It DD PPE CAUTION pin, the IRQ/CE pin must be pulled high to avoid acci- PPE ELAT EXCOL EXROW — STBY pin during PPE pin has a high voltage detect circuit $002B 1 Bit 0 — EPGM 0 0 MOTOROLA 19 , ...

Page 20

... EXROW can be written in special modes only. Bits [2:1] —Not implemented Always read zero EPGM —EPROM Programming Voltage Enable EPGM can be read any time and can only be written when ELAT = Programming voltage to EPROM array disconnected 1 = Programming voltage to EPROM array connected MOTOROLA 20 M68HC11 K Series MC6HC11KTS/D ...

Page 21

... EXTAL XTAL XOUT E TESTxx (3) MODA/LIR MODB/V STBY RESET NOTE 2 UNUSED INPUTS GND GND GND GND GND GND NOTE 1 GND GND GND GND GND UNUSED NOTE 3 OUTPUTS GND GND NOTE 4 GND MOTOROLA 21 ...

Page 22

... EEON bit in the CONFIG register. EEPROM can be placed at any 4-Kbyte bound- ary ($xD80) by writing appropriate values to the INIT2 register. Note that EEPROM can be mapped so that it contains the vector space. Refer to Figure 4. The MC68HC11K0, MC68HC11K3, MC68L11K0, and MC68L11K3 have no EEPROM. Refer to the ordering information tables. ...

Page 23

... LVPEN bit in DD ROW Action 0 Bulk Erase (All 640 Bytes) 1 Row Erase (16 Bytes) 0 Byte Erase 1 Byte Erase PTCON BPRT3 BPRT2 NOTE has fallen below a safe operating $0035 1 Bit 0 BPRT1 BPRT0 1 1 MOTOROLA 23 ...

Page 24

... Unused bits always read as ones. In normal modes (SMOD = 0), CONFIG bits can only be written using the EEPROM programming se- quence, and are neither readable nor active until latched via the next reset. In special modes (SMOD = 1), CONFIG bits can be written at any time. MOTOROLA 24 Block Protected Block Size $xF80– ...

Page 25

... Although the security feature can easily be disabled when in bootstrap mode, the bootloader firmware residing in bootstrap ROM checks to see if the NOSEC bit is clear. If NOSEC is clear (security enabled), the bootloader program performs the following: M68HC11 K Series MC6HC11KTS CLKX PAREN NOSEC NOCOP — — — — $003F 1 Bit 0 ROMON EEON — — MOTOROLA 25 ...

Page 26

... At this time, devices with the security enhancement are only available as one-time-programmable (OTP) MCUs in non-windowed packages. Once they have been programmed and secured, they will not function in bootstrap mode. For more information refer to M68HC11 Reference Manual (M68HC11RM/AD). MOTOROLA 26 M68HC11 K Series MC6HC11KTS/D ...

Page 27

... M68HC11 CPU beyond the physical 64 Kbyte limit of the 16 CPU address lines. The following is a brief description of how the extended addressing is achieved. For a more de- tailed discussion refer to application note Using the MC68HC11K4 Memory Mapping Logic (AN452/D). Memory expansion is achieved by manipulating the CPU address lines such that, even though the CPU cannot distinguish more than 64 Kbytes of physical memory Mbyte can be accessed through a paged memory scheme ...

Page 28

... Kbytes 32 Kbytes (Window Based at $4000) ADDR[14:0] ADDR[13:0] XA15 XA[15:14] ADDR[14:0] ADDR[13:0] XA[16:15] XA[16:14] ADDR[14:0] ADDR[13:0] XA[17:15] XA[17:14] ADDR[14:0] ADDR[13:0] XA[18:15] XA[18:14] — — — — — — — — $002D 2 1 Bit 0 PGAR1 PGAR0 $0056 2 1 Bit 0 — W1SZ1 W1SZ0 M68HC11 K Series MC68HC11KTS/D ...

Page 29

... X1A18 X1A17 $0059 — X2A18 X2A17 RESET M68HC11 K Series MC68HC11KTS/D Window Size Window disabled 8 K —Window can have 8-Kbyte banks 16 K —Window can have 16-Kbyte banks 32 K —Window can have 32-Kbyte banks — W1A15 ...

Page 30

... Kbyte memory space or in the expanded memory space. Chip select signals are a shared func- tion of port H. When an MCU pin is not used for chip select functions it can be used for general-purpose I/O. The following table contains a summary of the attributes of each chip select that can be controlled by user software. MOTOROLA 30 M68HC11 K Series MC68HC11KTS/D ...

Page 31

... Kbyte size located at addresses $0000 to $1FFF. Polarity of the active state is programmable for active high or active low. Clock stretching can be set from zero to three cycles. M68HC11 K Series MC68HC11KTS/D IOEN in CSCTL —1 = On, off at reset (0) IOCSA in CSCTL —1 = Address valid valid IOPL in CSCTL —1 = Active high Active low IOSZ in CSCTL — ...

Page 32

... Priority GPCS1 GPCS1 GPCS2 GPCS1 GCSPR = 1 On-Chip Registers On-Chip RAM Bootloader ROM On-Chip EEPROM On-Chip ROM/EPROM I/O Chip Select GP Chip Select 1 GP Chip Select 2 Program Chip Select IOCSA IOSZ GCSPR PCSEN $005B 2 1 Bit 0 PCSZA PCSZB M68HC11 K Series MC68HC11KTS/D ...

Page 33

... GPCS1A —General-Purpose Chip Select 1 Address Bit 7 6 G1A18 G1A17 RESET G1A[18:11] —General-Purpose Chip Select 1 Address Selects the starting address of general-purpose chip select 1 range. Refer to the G1SZA–G1SZD table. M68HC11 K Series MC68HC11KTS/D PCSZB Size (Bytes ...

Page 34

... None None ADDR[15:11] G1A[18:11] ADDR[15:12] G1A[18:12] ADDR[15:13] G1A[18:13] ADDR[15:14] G1A[18:14] ADDR15 G1A[18:15] None G1A[18:16] None G1A[18:17] None G1A18 None None None None None None None None $005E 2 1 Bit 0 G2A12 G2A11 $005F 2 1 Bit 0 G2SZC G2SZD M68HC11 K Series MC68HC11KTS/D ...

Page 35

... Kbytes each. In this example, a total of 64 Kbytes is added to the address range of the MCU. Three of the expansion address lines (XA[15:13]) are used. Register values particular to this example are given below the diagram. M68HC11 K Series MC68HC11KTS/D Valid Bits D Size (Bytes) ...

Page 36

... WINDOW KBYTES, WINDOW 2 DISABLED CSCTL = $00 NO I/O OR PROGRAM CHIP SELECTS GPCS1A = $00 GEN. PURPOSE CHIP SELECT 1 FROM $00000 GPSC1C = $06 64 KBYTE RANGE (8 X 8K) GPCS2A = $00 N/A GPCS2C = $00 GEN. PURPOSE CHIP SELECT 2 DISABLED $0A000 $0C000 $0E000 BANK 5 BANK 6 BANK 7 XA[15:13]= XA[15:13]= XA[15:13]= 1:0:1 1:1:0 1:1:1 $0BFFF $0DFFF $0FFFF M68HC11 K Series MC68HC11KTS/D ...

Page 37

... CHIP SELECT 2 $00000 $A000 $C000 INTERNAL BANK 0 EPROM XA[17:14]= $FFFF 0:0:0:0 $03FFF PGAR = $1F XA[17:13] MMWBR = $84 WINDOW 1 @ $4000, WINDOW 2 @ $8000 MMSIZ = $E1 WINDOW KBYTES, WINDOW KBYTES Figure 8 Memory Expansion Example 2 M68HC11 K Series MC68HC11KTS/D WINDOW 1 $04000 $06000 $08000 $02000 BANK 1 BANK 2 BANK 3 BANK 4 XA[15:13]= XA[15:13]= XA[15:13]= XA[15:13]= 0:0:1 0:1:0 0:1:1 1:0:0 $03FFF $05FFF $07FFF ...

Page 38

... SCI status register to check for receive errors, then to read the received data from the SCI data register. These two steps satisfy the automatic clearing mechanism without requiring any special instructions. Refer to the following table for a list of interrupt and reset vector assignments. MOTOROLA 38 M68HC11 K Series MC68HC11KTS/D ...

Page 39

... IRQE —IRQ Select Edge Sensitive Only 0 = Low level recognition 1 = Falling edge recognition DLY —Enable Oscillator Start-Up Delay on Exit from STOP stabilization delay on exit from STOP 1 = Stabilization delay enabled on exit from STOP M68HC11 K Series MC68HC11KTS/D Interrupt Source CCR Mask IRQE* ...

Page 40

... MHz 3.0 MHz MDA* PSEL4 PSEL3 PSEL2 — XTAL = 16.0 MHz Timeout –0 ms, +8.2 ms 8.192 ms 32.768 ms 131.07 ms 524.29 ms 4.0 MHz $003A 1 Bit $003C 1 Bit 0 PSEL1 PSEL0 1 0 M68HC11 K Series MC68HC11KTS/D ...

Page 41

... X M68HC11 K Series MC68HC11KTS Interrupt Source Promoted X X Reserved (Default to IRQ Reserved (Default to IRQ Reserved (Default to IRQ IRQ 1 1 Real-Time Interrupt 0 0 Timer Input Capture Timer Input Capture 2 ...

Page 42

... DDA3 DDA2 Shared Functions Timer High Order Address Data Bus SCI and SPI A/D Converter Low Order Address Memory Expansion PWM, Chip Select $0000 1 Bit 0 PA1 PA0 IC2 IC3 — — $0001 1 Bit 0 DDA1 DDA0 0 0 M68HC11 K Series MC68HC11KTS/D ...

Page 43

... Bit 7 6 DDC7 DDC6 RESET DDC[7:0] —Data Direction for Port C. Refer to CWOM bit in OPT2 register description that follows Corresponding pin configured for input 1 = Corresponding pin configured for output M68HC11 K Series MC68HC11KTS PB5 PB4 PB3 PB2 PB5 PB4 PB3 ...

Page 44

... PD5 PD4 PD3 PD2 SCK MOSI MISO DDD5 DDD4 DDD3 DDD2 NOTE $0038 1 Bit 0 XDV1 XDV0 0 0 $0008 1 Bit 0 PD1 PD0 TxD RxD $0009 1 Bit 0 DDD1 DDD0 0 0 M68HC11 K Series MC68HC11KTS/D ...

Page 45

... M —Mode (Select Character Format) Refer to 7 Serial Communications Interface. WAKE —Wakeup by Address Mark/Idle Refer to 7 Serial Communications Interface. ILT —Idle Line Type Refer to 7 Serial Communications Interface. PE —Parity Enable Refer to 7 Serial Communications Interface. M68HC11 K Series MC68HC11KTS MSTR CPOL CPHA SPR1 ...

Page 46

... Bit 0 PE1 PE0 I I AN1 AN0 $0003 2 1 Bit 0 DDF1 DDF0 $0005 2 1 Bit 0 PF1 PF0 PF1 PF0 ADDR1 ADDR0 $007C 2 1 Bit 0 PH1 PH0 PW2 PW1 $007D 2 1 Bit 0 DDH1 DDH0 M68HC11 K Series MC68HC11KTS/D ...

Page 47

... In this case, data direction bits are not changed and have no effect on these lines. DDRG reverts to controlling the I/O state of a pin when the associated function is disabled. Refer to 4.1 Memory Ex- pansion for further information. M68HC11 K Series MC68HC11KTS/D NOTE ...

Page 48

... Port x pin on-chip pull-up devices disabled 1 = Port x pin on-chip pull-up devices enabled FPPUE and BPPUE have no effect in expanded mode because port F and port B are address outputs. MOTOROLA — — HPPUE GPPUE NOTE $002C 1 Bit 0 FPPUE BPPUE 1 1 M68HC11 K Series MC68HC11KTS/D ...

Page 49

... The enhanced baud rate generator is shown in the following diagram. Refer to Table 7 for standard val- ues. 13-BIT COUNTER EXTAL 13-BIT COMPARE SCBDH/L SCI BAUD CONTROL Figure 9 SCI Baud Generator Circuit Diagram M68HC11 K Series MC68HC11KTS/D INTERNAL PHASE 2 CLOCK RESET SYNCH = 2 RECEIVER BAUD RATE ...

Page 50

... SCI INTERRUPT REQUESTS REQUEST Figure 10 SCI Transmitter Block Diagram MOTOROLA 50 (WRITE ONLY) 8 FORCE PIN DIRECTION (OUT) TRANSMITTER CONTROL LOGIC SCSR INTERRUPT STATUS TDRE TIE TC TCIE SCCR2 SCI CONTROL 2 DDD1 PIN BUFFER PD1 AND CONTROL TxD 8 8 INTERNAL DATA BUS M68HC11 K Series MC68HC11KTS/D ...

Page 51

... DISABLE DRIVER SCSR2 SCI STATUS 2 M WAKE-UP LOGIC SCCR1 SCI CONTROL 1 SCI Tx SCI INTERRUPT REQUESTS REQUEST Figure 11 SCI Receiver Block Diagram M68HC11 K Series MC68HC11KTS SHIFT REGISTER DATA ( RECOVERY RE PARITY DETECT SCSR1 SCI STATUS 1 RDRF RIE IDLE ...

Page 52

... Bit 0 SBR8 High 0 0 SBR0 Low MHz Dec Value Hex Value 4545 $11C1 3333 $0D05 1666 $0682 833 $0341 416 $01A0 208 $00D0 104 $0068 52 $0034 26 $001A 13 $000D $0072 Bit Bootstrap Mode 0 Other Modes M68HC11 K Series MC68HC11KTS/D ...

Page 53

... RDRF and OR interrupts disabled 1 = SCI interrupt requested when RDRF flag or the OR status flag is set ILIE —Idle Line Interrupt Enable 0 = IDLE interrupts disabled 1 = SCI interrupt requested when IDLE status flag is set TE —Transmitter Enable 0 = Transmitter disabled 1 = Transmitter enabled M68HC11 K Series MC68HC11KTS RIE ILIE TE RE ...

Page 54

... FE —Framing Error FE is set when a zero is detected where a stop bit was expected. Clear the FE flag by reading SCSR1 and then reading SCDR Stop bit detected 1 = Zero detected MOTOROLA RDRF IDLE $0074 2 1 Bit M68HC11 K Series MC68HC11KTS/D ...

Page 55

... Ninth serial data bit received when SCI is configured for nine-data-bit operation. T8 —Transmitter Bit 8 Ninth serial data bit transmitted when SCI is configured for nine-data-bit operation. Bits [5:0] —Not implemented Always read zero R/T[7:0] —Receiver/Transmitter Data Bits [7:0] SCI data is double buffered in both directions. M68HC11 K Series MC68HC11KTS — — — ...

Page 56

... MOTOROLA 56 MSB LSB 8-BIT SHIFT REGISTER READ DATA BUFFER CLOCK CLOCK LOGIC MSTR SPE SPIE SPCR SPI CONTROL REGISTER INTERNAL DATA BUS Figure 12 SPI Block Diagram MISO/ S PD2 M MOSI/ M PD3 S PIN CONTROL LOGIC S SCK/ PD4 M SS/ PD5 M68HC11 K Series MC68HC11KTS/D ...

Page 57

... SCK (CPOL = 1) SAMPLE INPUT (CPHA = 0) DATA OUT MSB SAMPLE INPUT (CPHA = 1) DATA OUT MSB SS (TO SLAVE) This figure shows transmission order when LSBF = 0 default. If LSBF = 1, data is transferred in reverse order (LSB first). M68HC11 K Series MC68HC11KTS MSTR CPOL CPHA ...

Page 58

... MHz (Baud) 3.0 MHz 4.0 MHz 750 kHz 1.0 MHz 187.5 kHz 250 kHz 93.75 kHz 125 kHz 375 kHz 500 kHz 187.5 kHz 250 kHz 46.875 kHz 62.5 kHz 23.438 kHz 31.25 kHz $0029 1 Bit 0 — — $002A 1 Bit 0 1 Bit 0 M68HC11 K Series MC68HC11KTS/D ...

Page 59

... SPI data transferred MSB first 1 = SPI data transferred LSB first SPR2 —SPI Clock (SCK) Rate Select Adds a divide by four prescaler to SPI clock chain. Refer to SPCR register. XDV[1:0] —XOUT Clock Divide Select Refer to 2 Operating Modes. M68HC11 K Series MC68HC11KTS — IRVNE ...

Page 60

... Dedicated lines V and MOTOROLA 60 8-BIT CAPACITIVE DAC WITH SAMPLE AND HOLD SUCCESSIVE APPROXIMATION REGISTER AND CONTROL ADCTL A/D CONTROL RESULT REGISTER INTERFACE ADDR 2 A/D RESULT 2 ADDR 3 A/D RESULT 3 provide the reference supply voltage inputs INTERNAL DATA BUS ADDR 4 A/D RESULT 4 M68HC11 K Series MC68HC11KTS/D ...

Page 61

... Figure 15 Timing Diagram for a Sequence of Four A/D Conversions INPUT PROTECTION DEVICE ANALOG INPUT PIN < This analog switch is closed only during the 12-cycle sample time. Figure 16 Electrical Model of an Analog Input Pin (Sample Mode) M68HC11 K Series MC68HC11KTS/D MSB BIT 6 BIT 5 BIT 4 BIT CYCLES ...

Page 62

... Bit Result in ADRx if MULT = 1 ADR1 ADR2 ADR3 ADR4 ADR1 ADR2 ADR3 ADR4 — — — — * ADR1 ADR2 * ADR3 ADR4 $0031 – $0034 2 1 Bit 0 ADR1 2 1 Bit 0 ADR2 2 1 Bit 0 ADR3 2 1 Bit 0 ADR4 M68HC11 K Series MC68HC11KTS/D ...

Page 63

... Refer to 5 Resets and Interrupts CME —Clock Monitor Enable Refer to 5 Resets and Interrupts FCME —Force Clock Monitor Enable Refer to 5 Resets and Interrupts CR[1:0] —COP Timer Rate Select Refer to 10 Main Timer M68HC11 K Series MC68HC11KTS IRQE* DLY* CME FCME* ...

Page 64

... M68HC11 K Series MC68HC11KTS/D ...

Page 65

... LATCH CLK I4/O5 16-BIT LATCH CLK TIC1 (HI) TIC1 (LO) 16-BIT LATCH CLK TIC2 (HI) TIC2 (LO) 16-BIT LATCH CLK TIC3 (HI) TIC3 (LO) M68HC11 K Series MC68HC11KTS/D TCNT (HI) TCNT (LO) TOI 16-BIT FREE-RUNNING TOF COUNTER TAPS FOR RTI, COP WATCHDOG AND PULSE ACCUMULATOR TMSK1 OC1I TFLG1 CFORC OC1F FOC1 ...

Page 66

... Bit 0 — — — $000D 2 1 Bit 0 — — — $000E, $000F Bit 8 High TCNT Bit 0 Low $0010–$0015 Bit 8 High TIC1 Bit 0 Low Bit 8 High TIC2 Bit 0 Low Bit 8 High TIC3 Bit 0 Low M68HC11 K Series MC68HC11KTS/D ...

Page 67

... RESET OM[5:2] —Output Mode OL[5:2] —Output Level OMx TCTL2 —Timer Control 2 Bit 7 6 EDG4B EDG4A EDG1B RESET Table 11 Timer Control Configuration EDGxB M68HC11 K Series MC68HC11KTS ...

Page 68

... MOTOROLA OC4I I4/O5I IC1I OC3F OC4F I4/O5F IC1F NOTE PAOVI PAII — — $0022 1 Bit 0 IC2I IC3I 0 0 $0023 2 1 Bit 0 IC2F IC3F $0024 2 1 Bit 0 PR1 PR0 M68HC11 K Series MC68HC11KTS/D ...

Page 69

... Bit 7 6 — PAEN PAMOD RESET Bit 7 —Not implemented Always read zero PAEN —Pulse Accumulator System Enable Refer to 11 Pulse Accumulator. PAMOD —Pulse Accumulator Mode Refer to 11 Pulse Accumulator. M68HC11 K Series MC68HC11KTS/D NOTE PR[1:0] Prescaler ...

Page 70

... Period Length E = 2.0 MHz 4.096 ms E 8.192 ms 16.384 ms 32.768 2.0 MHz 13 244.141 Hz 14 122.070 Hz 61.035 30.518 3.0 MHz E = 4.0 MHz 2.731 ms 2.048 ms 5.461 ms 4.096 ms 10.923 ms 8.192 ms 21.845 ms 16.383 ms Frequency E = 3.0 MHz E = 4.0 MHz 366.211 Hz 488.281 Hz 183.105 Hz 244.141 Hz 91.553 Hz 122.070 Hz 45.776 Hz 61.035 Hz M68HC11 K Series MC68HC11KTS/D ...

Page 71

... AND OC1 EDGE DETECTOR OUTPUT BUFFER FROM MAIN TIMER OC1 FROM PACTL CONTROL DDRA7 Figure 18 Pulse Accumulator System Block Diagram M68HC11 K Series MC68HC11KTS/D Common XTAL Frequencies 8.0 MHz 12.0 MHz 2.0 MHz 3.0 MHz 500 ns 333 ns Pulse Accumulator (Gated Mode) 32.0 s 21.33 s 8.192 ms 5.461 ms TFLG2 INTERRUPT STATUS ...

Page 72

... Set each time a selected active edge is detected on the PAI input line Bits [3:0] —Not implemented Always read zero MOTOROLA PAOVI PAII — NOTE PAOVF PAIF — $0024 2 1 Bit 0 — PR1 PR0 $0025 2 1 Bit 0 — — — M68HC11 K Series MC68HC11KTS/D ...

Page 73

... PAIF. I4/O5 —Input Capture 4/Output Compare 5 Refer to 10 Main Timer. RTR[1:0] —Real-Time Interrupt Rate Refer to 10 Main Timer. PACNT —Pulse Accumulator Counter Bit 7 6 Bit 7 6 Can be read and written. M68HC11 K Series MC68HC11KTS PEDGE — I4/ ...

Page 74

... MHz, PWM periods greater than one minute are possible. In 16-bit mode, duty cycle resolution of almost 15 parts per million can be achieved (at a PWM frequen about 60 Hz). In the same system, a PWM frequency of 1 kHz corresponds to a duty cycle reso- lution of 0.025%. MOTOROLA 74 M68HC11 K Series MC68HC11TS/D ...

Page 75

... PWDTY4 PWM OUTPUT PWDTY PWPER CLOCK S 2 CLOCK A PWEN1 CLOCK PWEN2 SELECT CON12 CNT1 CNT2 PPOL1 Q PH0/ MUX BIT 0 PW1 Q Q PH1/ MUX BIT 1 PW2 Q PPOL2 PORT H PIN CONTROL PPOL3 Q PH2/ MUX BIT 2 PW3 Q Q PH3/ MUX BIT 3 PW4 Q PPOL4 MOTOROLA 75 ...

Page 76

... PCKB[3:1] —Prescaler for Clock B Determines the rate for clock B PWPOL —Pulse-Width Modulation Timer Polarity Bit 7 6 PCLK4 PCLK3 RESET PCLK4 —Pulse-Width Channel 4 Clock Select 0 = Clock B is source 1 = Clock S is source MOTOROLA PCKA2 PCKA1 — PCKB3 PCKA[2:1] Value of Clock A ...

Page 77

... PWEN4 PWEN3 $0062 1 Bit $0063 1 Bit 0 PWEN2 PWEN1 0 0 $0064–$0067 Bit 0 PWCNT1 Bit 0 PWCNT2 Bit 0 PWCNT3 Bit 0 PWCNT4 0 MOTOROLA 77 ...

Page 78

... The following conditions always cause the corresponding output to be high: PWDTYx = $00, PWPERx > $00, and PPOLx = 0 PWDTYx PWPERx, and PPOLx = 1 PWPERx = $00 and PPOLx = 1 The following conditions always cause the corresponding output to be low: PWDTYx = $00, PWPERx > $00, and PPOLx = 1 PWDTYx PWPERx, and PPOLx = 0 PWPERx = $00 and PPOLx = 0 MOTOROLA ...

Page 79

... M68HC11 K Series MC68HC11KTS/D MOTOROLA 79 ...

Page 80

... Mfax™: RMFAX0@email.sps.mot.com - TOUCHTONE (602) 244-6609 INTERNET: http://Design-NET.com JAPAN: Nippon Motorola Ltd.; Tatsumi-SPD-JLDC, 6F Seibu-Butsuryu-Center, 3-14-2 Tatsumi Koto-Ku, Tokyo 135, Japan. 81-3-3521-8315 ASIA PACIFIC: Motorola Semiconductors H.K. Ltd.; 8B Tai Ping Industrial Park, 51 Ting Kok Road, Tai Po, N.T., Hong Kong. 852-26629298 Mfax is a trademark of Motorola, Inc. MC68HC11KTS/D ...