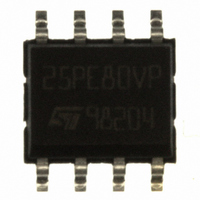

M25PE80-VMN6TP NUMONYX, M25PE80-VMN6TP Datasheet - Page 10

M25PE80-VMN6TP

Manufacturer Part Number

M25PE80-VMN6TP

Description

IC FLASH 8MBIT 75MHZ 8SOIC

Manufacturer

NUMONYX

Series

Forté™r

Datasheet

1.M25PE80-VMN6TP.pdf

(66 pages)

Specifications of M25PE80-VMN6TP

Format - Memory

FLASH

Memory Type

FLASH

Memory Size

8M (1M x 8)

Speed

75MHz

Interface

SPI, 3-Wire Serial

Voltage - Supply

2.7 V ~ 3.6 V

Operating Temperature

-40°C ~ 85°C

Package / Case

8-SOIC (3.9mm Width)

Package

8SOIC N

Cell Type

NOR

Density

8 Mb

Architecture

Sectored

Block Organization

Symmetrical

Typical Operating Supply Voltage

3.3 V

Sector Size

256Byte x 4096

Timing Type

Synchronous

Interface Type

Serial-SPI

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Other names

M25PE80-VMN6TPTR

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

M25PE80-VMN6TP

Manufacturer:

ST

Quantity:

6 000

Part Number:

M25PE80-VMN6TP

Manufacturer:

ST

Quantity:

20 000

SPI modes

3

10/66

SPI modes

These devices can be driven by a microcontroller with its SPI peripheral running in either of

the two following modes:

For these two modes, input data is latched in on the rising edge of serial clock (C), and

output data is available from the falling edge of serial clock (C).

The difference between the two modes, as shown in

bus master is in standby mode and not transferring data:

Figure 4.

1. The Top Sector Lock (TSL) signal in the T7Y process, or the Write Protect (W) signal in the T9HX process,

Figure 4

device is selected at a time, so only one device drives the serial data output (Q) line at a

time, the other devices are high impedance. Resistors R (represented in

that the M25PE80 is not selected if the bus master leaves the S line in the high impedance

state. As the bus master may enter a state where all inputs/outputs are in high impedance at

the same time (for example, when the bus master is reset), the clock line (C) must be

connected to an external pull-down resistor so that, when all inputs/outputs become high

impedance, the S line is pulled High while the C line is pulled Low (thus ensuring that S and

C do not become High at the same time, and so, that the t

typical value of R is 100 kΩ, assuming that the time constant R*C

capacitance of the bus line) is shorter than the time during which the bus master leaves the

SPI bus in high impedance.

SPI interface with

(CPOL, CPHA) =

CS3

should be driven, High or Low as appropriate.

(0, 0) or (1, 1)

SPI bus master

CPOL=0, CPHA=0

CPOL=1, CPHA=1

C remains at 0 for (CPOL=0, CPHA=0)

C remains at 1 for (CPOL=1, CPHA=1)

shows an example of three devices connected to an MCU, on an SPI bus. Only one

CS2 CS1

Bus master and memory devices on the SPI bus

SDO

SDI

SCK

R

R

C Q D

S

SPI memory

device

W

or

TSL

V

CC

Reset

V

R

SS

C Q D

S

Figure

SPI memory

device

SHCH

W

or

TSL

5, is the clock polarity when the

V

CC

Reset

requirement is met). The

p

V

R

SS

(C

p

= parasitic

C Q D

Figure

S

SPI memory

device

4) ensure

W

or

TSL

M25PE80

V

CC

Reset

AI13558b

V

V

V

SS

CC

SS