EPC16UC88 Altera, EPC16UC88 Datasheet - Page 25

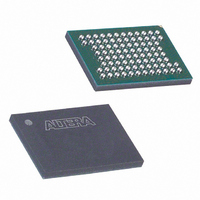

EPC16UC88

Manufacturer Part Number

EPC16UC88

Description

IC CONFIG DEVICE 16MBIT 88-UBGA

Manufacturer

Altera

Series

EPCr

Datasheet

1.EPC8QC100.pdf

(34 pages)

Specifications of EPC16UC88

Programmable Type

In System Programmable

Memory Size

16Mb

Voltage - Supply

3 V ~ 3.6 V

Operating Temperature

0°C ~ 70°C

Package / Case

88-UBGA

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

Other names

544-1228

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

EPC16UC88

Manufacturer:

ALTERA

Quantity:

62

Company:

Part Number:

EPC16UC88

Manufacturer:

ALTERA

Quantity:

275

Part Number:

EPC16UC88

Manufacturer:

ALTERA/阿尔特拉

Quantity:

20 000

Company:

Part Number:

EPC16UC888N

Manufacturer:

ALTERA

Quantity:

621

Company:

Part Number:

EPC16UC88AA

Manufacturer:

ALTERA

Quantity:

280

Part Number:

EPC16UC88AA

Manufacturer:

ALTERA

Quantity:

20 000

Part Number:

EPC16UC88N

Manufacturer:

ALTERA/阿尔特拉

Quantity:

20 000

Chapter 1: Enhanced Configuration Devices (EPC4, EPC8, and EPC16) Data Sheet

Power-On Reset

Power-On Reset

Power Sequencing

© December 2009 Altera Corporation

1

1

The POR circuit keeps the system in reset until power-supply voltage levels have

stabilized. The POR time consists of the V

POR delay counter. When the supply is stable and the POR counter expires, the POR

circuit releases the OE pin. The POR time can be further extended by an external

device by driving the OE pin low.

Do not execute JTAG or ISP instructions until POR is complete.

The enhanced configuration device supports a programmable POR delay setting. You

can set the POR delay to the default 100-ms setting or reduce the POR delay to 2 ms

for systems that require fast power-up. The PORSEL input pin controls this POR

delay; a logic-high level selects the 2-ms delay, while a logic-low level selects the

100-ms delay.

The enhanced configuration device can enter reset under the following conditions:

■

■

■

Altera requires that you power-up the FPGA's V

configuration device's POR expires.

Power up needs to be controlled so that the enhanced configuration device’s OE signal

goes high after the CONF_DONE signal is pulled low. If the EEPC device exits POR

before the FPGA is powered up, the CONF_DONE signal will be high because the

pull-up resistor is holding this signal high. When the enhanced configuration device

exits POR, OE is released and pulled high by a pull-up resistor. Since the enhanced

configuration device samples the nCS signal on the rising edge of OE, it detects a high

level on CONF_DONE and enters an idle mode. DATA and DCLK outputs will not toggle

in this state and configuration will not begin. The enhanced configuration device will

only exit this mode if it is powered down and then powered up correctly.

To ensure the enhanced configuration device enters configuration mode properly, you

must ensure that the FPGA completes power-up before the enhanced configuration

device exits POR.

The pin-selectable POR time feature is useful for ensuring this power-up sequence.

The enhanced configuration device has two POR settings, 2 ms when PORSEL is set to

a high level and 100 ms when PORSEL is set to a low level. For more margin, the

100-ms setting can be selected to allow the FPGA to power-up before configuration is

attempted.

The POR reset starts at initial power-up during V

below the minimum operating condition anytime after V

The FPGA initiates reconfiguration by driving nSTATUS low, which occurs if the

FPGA detects a CRC error or if the FPGA’s nCONFIG input pin is asserted

The controller detects a configuration error and asserts OE to begin

re-configuration of the Altera FPGA (for example, when CONF_DONE stays low

after all configuration data has been transmitted)

CC

ramp time and a user-programmable

Configuration Handbook (Complete Two-Volume Set)

CCINT

CC

supply before the enhanced

ramp-up or if V

CC

has stabilized

CC

drops

1–25