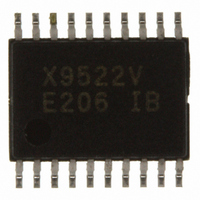

X9522V20I-B Intersil, X9522V20I-B Datasheet

X9522V20I-B

Specifications of X9522V20I-B

Related parts for X9522V20I-B

X9522V20I-B Summary of contents

Page 1

... CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures. | 1-888-INTERSIL or 1-888-468-3774 Intersil (and design registered trademark of Intersil Americas Inc. ©2000 Intersil Inc., Patents Pending. Copyright Intersil Americas Inc. 2006, 2010. All Rights Reserved All other trademarks mentioned are the property of their respective owners. X9522 FN8208.2 ...

Page 2

... Ordering Information PART NUMBER PART MARKING X9522V20I-A X9522VIA X9522V20I-B X9522VIB X9522V20IZ-A (Note) X9522VZIA X9522V20IZ-B (Note) X9522VZIB *Add "T1" suffix for tape and reel. NOTE: Intersil Pb-free plus anneal products employ special Pb-free material sets; molding compounds/die attach materials and 100% matte tin plate termination finish, which are RoHS compliant and compatible with both SnPb and Pb-free soldering operations ...

Page 3

... STAT) register bits. The status of these two moni- tor outputs can be read out via the 2-wire serial port. Intersil’s unique circuits allow for all internal trip voltages to be individually programmed with high accuracy. This gives the designer great flexibility in changing system parameters, either at the time of manufacture the field ...

Page 4

PIN ASSIGNMENT Pin Name R 1 Connection to end of resistor array for (the 256 Tap) DCP Connection to terminal equivalent to the “Wiper” mechanical potentiometer for DCP Connection to ...

Page 5

SCL SDA Figure 1. PRINCIPLES OF OPERATION SERIAL INTERFACE Serial Interface Conventions The device supports a bidirectional bus oriented protocol. The protocol defines any device that sends data onto the bus as a transmitter, and the receiving device as the ...

Page 6

DEVICE INTERNAL ADDRESSING SCL SCL from from Master Master Data Output from Transmitter Data Output from Start Receiver Figure 3. Addressing Protocol Overview The user addressable internal components of the X9522 can be split up into two main parts: —Three ...

Page 7

Nonvolatile Write Acknowledge Polling After a nonvolatile write command sequence (for either the Non Volatile Memory of a DCP (NVM), or the CONSTAT Register) has been correctly issued (including the final STOP condition), the X9522 ini- tiates an internal high ...

Page 8

Vcc t trans 0 The data in the WCR is then decoded to select and enable one of the respective FET switches. A “make before break” sequence is used internally for the FET switches when the wiper is moved from ...

Page 9

Address is 0), the Most Significant Bit of the Instruction Byte (I7), determines the Write Type (WT) performed WRITE TYPE † WT Description Select a Volatile Write operation to ...

Page 10

Next, an Instruction Byte is issued on SDA. Bits P1 and P0 of the Instruction Byte determine which WCR written, while the WT bit determines if the Write volatile or nonvolatile. If the Instruction ...

Page 11

S t Signals from Slave a the Master Address r t SDA Bus Signals from the Slave Following this ACKNOWLEDGE, the master imme- diately issues another START condition and a valid Slave address ...

Page 12

SCL SDA SLAVE ADDRESS BYTE T Figure 12. CONSTAT Register Write Command Sequence The WEL bit is a volatile latch that powers up in the disabled, LOW (0) state. ...

Page 13

CONSTAT Register Write Operation The CONSTAT register is accessed using the Slave Address set to 1010010 (Refer to Figure 4.). Following the Slave Address Byte, access to the CONSTAT register requires an Address Byte which must be set to FFh. ...

Page 14

DATA PROTECTION There are a number of levels of data protection features designed into the X9522. Any write to the device first requires setting of the WEL bit in the CONSTAT register. A write to the CONSTAT regis- ter itself, ...

Page 15

V2 SCL SDA † A0h Figure 15. Setting V V3 monitoring The X9522 asserts the V3RO output HIGH if the voltage V3 exceeds the corresponding ...

Page 16

Setting a Higher V Voltage (x = 2,3) TRIPx To set a V threshold to a new voltage which TRIPx is higher than the present threshold, the user must apply the desired V threshold voltage to the TRIPx corresponding input ...

Page 17

New Vx applied = + Old Vx applied | Error | Figure 17. V Using this process, the desired accuracy for a particu- lar V threshold may be attained using a succes- TRIPx sive number of iterations. 17 X9522 V ...

Page 18

ABSOLUTE MAXIMUM RATINGS Temperature under Bias Storage Temperature Voltage on WP pin (With respect to Vss) Voltage on other pins (With respect to Vss) | Voltage Voltage D.C. Output Current (SDA,V2RO,V3RO) Lead Temperature ...

Page 19

TIMING DIAGRAMS Figure 20. Bus Timing t F SCL t SU:DAT t SU:SA t HD:STA SDA IN SDA OUT Figure 21. WP Pin Timing START SCL SDA IN t SU:WP WP Figure 22. Write Cycle Timing SCL 8th bit of ...

Page 20

Figure 23. V2, V3 Timing Diagram RPDx VxRO Vcc / V1 Note : x = 2,3. Figure 24. V Programming Timing Diagram (x = 2,3) TRIPX V2 TSU VPS SCL ...

Page 21

Figure 25. DCP “Wiper Position” Timing Rwx (x = 0,1,2) R wx( tap position SCL SDA SLAVE ADDRESS BYTE T 21 X9522 ...

Page 22

D.C. OPERATING CHARACTERISTICS Symbol Parameter Current into Vcc / V1 Pin (1) I CC1 Read memory array Write nonvolatile memory Current into Vcc / V1 Pin (2) I CC2 With 2-Wire bus activity Input Leakage Current I LI Input Leakage ...

Page 23

A.C. CHARACTERISTICS (See Figure 20, Figure 21, Figure 22) Symbol f SCL Clock Frequency SCL (5) t Pulse width Suppression Time at inputs IN (5) t SCL LOW to SDA Data Out Valid AA (5) t Time the bus free ...

Page 24

POTENTIOMETER CHARACTERISTICS Symbol Parameter R End to End Resistance Tolerance TOL V R Terminal Voltage (x = 0,1,2) RHx Terminal Voltage (x = 0,1,2) RLx L (1)(6 P Power Rating ) R R DCP Wiper Resistance W ...

Page 25

1,2) PROGRAMMING PARAMETERS (See Figure 24) TRIPX Parameter t V Program Enable Voltage Setup time VPS TRIPx t V Program Enable Voltage Hold time VPH TRIPx t V Setup time TSU TRIPx t V Hold (stable) time ...

Page 26

APPENDIX 1 DCP1 (100 Tap) Tap position to Data Byte translation Table Tap Position Decimal ...

Page 27

APPENDIX 2 DCP1 (100 Tap) tap position to Data Byte translation algorithm example. (Example 1) unsigned DCP1_TAP_Position(int tap_pos) { int block; int i; int offset; int wcr_val; offset= 0; block = tap_pos / 25; if (block < 0) return ((unsigned)0); ...

Page 28

APPENDIX 2 DCP1 (100 Tap) tap position to Data Byte translation algorithm example. (Example 2) unsigned DCP100_TAP_Position(int tap_pos optional range checking */ if (tap_pos < 0) return ((unsigned)0); else if (tap_pos >99) return ((unsigned) 96); /* 100 Tap ...

Page 29

... Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use ...