CDB42448 Cirrus Logic Inc, CDB42448 Datasheet - Page 36

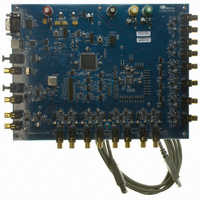

CDB42448

Manufacturer Part Number

CDB42448

Description

BOARD EVAL FOR CS42448 CODEC

Manufacturer

Cirrus Logic Inc

Specifications of CDB42448

Main Purpose

Audio, CODEC

Embedded

Yes, FPGA / CPLD

Utilized Ic / Part

CS42448

Primary Attributes

24-Bit, 192 kHz, 6 ADCs: 102dB Dynamic Range, 8 DACs: 105dB Dynamic Range

Secondary Attributes

Time Division Multiplexed (TDM), I2C, and SPI Interface, Popguard® Technology

Description/function

Audio CODECs

Operating Supply Voltage

5 V to 12 V

Product

Audio Modules

For Use With/related Products

CS42448

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

Lead Free Status / RoHS Status

Lead free / RoHS Compliant, Contains lead / RoHS non-compliant

Other names

598-1151

36

4.7.2

C C L K

CS

C D IN

C D O U T

SDA

SCL

I²C Mode

In I²C Mode, SDA is a bidirectional data line. Data is clocked into and out of the part by the clock, SCL.

There is no CS pin. Pins AD0 and AD1 form the two least-significant bits of the chip address and should

be connected through a resistor to VLC or DGND as desired. The state of the pins is sensed while the

CS42448 is being reset.

The signal timings for a read and write cycle are shown in

defined as a falling transition of SDA while the clock is high. A Stop condition is a rising transition while

the clock is high. All other transitions of SDA occur while the clock is low. The first byte sent to the

CS42448 after a Start condition consists of a 7-bit chip address field and a R/W bit (high for a read, low

for a write). The upper 5 bits of the 7-bit address field are fixed at 10010. To communicate with a CS42448,

the chip address field, which is the first byte sent to the CS42448, should match 10010 followed by the

settings of the AD1 and AD0. The eighth bit of the address is the R/W bit. If the operation is a write, the

next byte is the Memory Address Pointer (MAP) which selects the register to be read or written. If the op-

eration is a read, the contents of the register pointed to by the MAP will be output. Setting the auto-incre-

ment bit in MAP allows successive reads or writes of consecutive registers. Each byte is separated by an

acknowledge bit. The ACK bit is output from the CS42448 after each input byte is read, and is input to the

CS42448 from the microcontroller after each transmitted byte.

ADDRESS

MAP = Memory Address Pointer, 8 bits, MSB first

1001111

C H IP

START

0

1

CHIP ADDRESS (WRITE)

1

0

High Impedance

0

2

1

R/W

3

0 AD1 AD0 0

4

5

M A P

Figure 23. Control Port Timing in SPI Mode

6

Figure 24. Control Port Timing, I²C Write

7

ACK

8

MSB

b y te 1

INCR

9

10 11

6

DATA

MAP BYTE

5

12

4

b y te n

13 14 15

3

LSB

2

1

16 17 18

0

ACK

A D D R E S S

7

C H IP

1001111

19

6

DATA

Figure 24

24 25

1

0

ACK

R/W

26

27 28

7

MSB

and

DATA +1

6

Figure

1

0

LSB MSB

7

25. A Start condition is

DATA +n

6

1

0

ACK

CS42448

STOP

LSB

DS648F3