DM164120-1 Microchip Technology, DM164120-1 Datasheet - Page 14

DM164120-1

Manufacturer Part Number

DM164120-1

Description

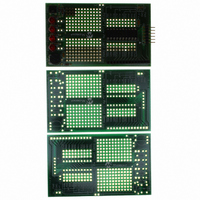

BOARD DEMO PICKIT 2 LP COUNT

Manufacturer

Microchip Technology

Type

MCUr

Datasheet

1.DM164120-1.pdf

(42 pages)

Specifications of DM164120-1

Contents

3 Boards (1 Populated, 2 Bare)

Processor To Be Evaluated

PIC16F690

Silicon Manufacturer

Microchip

Core Architecture

PIC

Core Sub-architecture

PIC16

Silicon Core Number

PIC16F

Silicon Family Name

PIC16F6xxx

Rohs Compliant

Yes

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

For Use With/related Products

28-pin PIC16C, 16F, 18C, 18F

Lead Free Status / Rohs Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

DM164120-1

Manufacturer:

Microchip Technology

Quantity:

135

Low Pin Count Demo Board User’s Guide

2.2

2.3

DS51556A-page 10

MEMORY ORGANIZATION

INSTRUCTION FORMATS

PICmicro

areas. This allows faster execution as the address and data busses are separate and

do not have to do double duty.

Data Memory is held in file registers. Instructions referring to file registers use 7 bits,

so only 128 file registers can be addressed. Multiple file registers are arranged into

“pages”. Two extra bits RP0 and RP1 (in the Status register) allow accessing multiple

pages. These two bits effectively become the top two bits of the file register address.

The additional pages may or may not be implemented, depending on the device.

Mid-range devices reserve the first 32 addresses of each page for Special Function

Registers (SFRs). SFRs are how the program interacts with the peripherals. The

controls and data registers are memory mapped into the SFR space. Addresses above

0x20 to the end of each page are General Purpose Registers (GPRs), where program

variables may be stored.

Some frequently used registers may be accessed from any bank. For example, the

Status register is always available no matter which bank is selected via the RP bits. The

last 16 bytes (0x70-0x7F) may also be accessed from any bank.

Program Memory is accessed via a 13-bit Program Counter (PC). The lower 8 bits are

accessible via SFR (PCL), and the upper 5 are at a PCLATH. See the

PIC16F685/687/689/690 Data Sheet’s (DS41262) Section on PCL and PCLATH for

more details on the PC. PCLATH becomes important when program memory size

exceeds 1k instructions, and also for the table look-up in Lesson 12.

Mid-range PICmicro

otherwise noted, the lessons in this manual use the Internal Oscillator running at 4 MHz.

Most instructions follow one of three formats: Byte oriented instructions, Bit oriented

instructions and Literal instructions.

Byte instructions contain 7-bit data address, a destination bit, and 6-bit op code. The

data address plus the RP0 and RP1 bits create a 9-bit data memory address for one

operand. The other operand is the Working register (called W or Wreg). After the

instruction executes, the destination bit (d) specifies whether the result will be stored in

W or back in the original file register. For example:

adds the contents of Wreg and data, with the result going back into data.

Bit instructions operate on a specific bit within a file register. They contain 7 bits of data

address, 3-bit number and the remaining 4 bits are op code. These instructions may

set or clear a specific bit within a file register. They may also be used to test a specific

bit within a file register. For example:

set the RP0 bit in the Status register.

Literal instructions contain the data operand within the instruction. The Wreg becomes

the other operand. Calls and GOTO’s use 11 bits as a literal address.

Moves the ASCII value of ‘A’ (0x41) into Wreg.

ADDWF data,f

BSF

MOVLW'A'

®

microcontrollers are designed with separate program and data memory

STATUS,RP0

®

MCUs may be clocked by a number of different devices. Unless

© 2005 Microchip Technology Inc.