DS21FF44 Maxim Integrated Products, DS21FF44 Datasheet - Page 39

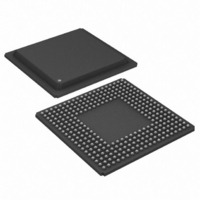

DS21FF44

Manufacturer Part Number

DS21FF44

Description

IC FRAMER E1 4X4 16CH 300-BGA

Manufacturer

Maxim Integrated Products

Datasheet

1.DS21FT44N.pdf

(117 pages)

Specifications of DS21FF44

Controller Type

E1 Framer

Interface

Parallel/Serial

Voltage - Supply

2.97 V ~ 3.63 V

Current - Supply

300mA

Operating Temperature

0°C ~ 70°C

Mounting Type

Surface Mount

Package / Case

300-BGA

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

- Current page: 39 of 117

- Download datasheet (692Kb)

constant Remote Alarm will be transmitted if the framer cannot find CRC4 multiframe synchronization

within 400ms as per G.706.

It is an illegal state to have both CCR2.4 and CCR2.5 set to one at the same time.

CCR3: COMMON CONTROL REGISTER 3 (Address = 1B Hex)

(MSB)

TESE

SYMBOL

TCBFS

TIRFS

RCLA

RSRE

THSE

TBCS

TESE

–

TCBFS

POSITION

CCR3.7

CCR3.6

CCR3.5

CCR3.4

CCR3.3

CCR3.2

CCR3.1

CCR3.0

TIRFS

Transmit Side Elastic Store Enable

0 = elastic store is bypassed

1 = elastic store is enabled

Transmit Channel Blocking Registers (TCBR) Function

Select

0 = TCBRs define the operation of the TCHBLK output pin

1 = TCBRs define which signaling bits are to be inserted

Transmit Idle Registers (TIR) Function Select. See Section

15 for details.

0 = TIRs define in which channels to insert idle code

1 = TIRs define in which channels to insert data from RSER

(i.e., Per Channel Loopback function)

Not Assigned. Should be set to zero when written.

Receive Side Signaling Reinsertion Enable. See Section 14

for details.

0 = do not reinsert signaling bits into the data stream presented

at the RSER pin

1 = reinsert the signaling bits into data stream presented at the

RSER pin

Transmit Side Hardware Signaling Insertion Enable. See

Section 14 for details.

0 = do not insert signaling from the TSIG pin into the data

stream presented at the TSER pin

1 = insert signaling from the TSIG pin into the data stream

presented at the TSER pin

Transmit Side Backplane Clock Select

0 = if TSYSCLK is 1.544MHz

1 = if TSYSCLK is 2.048MHz

Receive Carrier Loss (RCL) Alternate Criteria

0 = RCL declared upon 255 consecutive zeros (125µs)

1 = RCL declared upon 2048 consecutive zeros (1ms)

—

39 of 117

RSRE

NAME AND DESCRIPTION

THSE

TBCS

RCLA

(LSB)

Related parts for DS21FF44

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

MAX7528KCWPMaxim Integrated Products [CMOS Dual 8-Bit Buffered Multiplying DACs]

Manufacturer:

Maxim Integrated Products

Datasheet:

Part Number:

Description:

Single +5V, fully integrated, 1.25Gbps laser diode driver.

Manufacturer:

Maxim Integrated Products

Datasheet:

Part Number:

Description:

Single +5V, fully integrated, 155Mbps laser diode driver.

Manufacturer:

Maxim Integrated Products

Datasheet:

Part Number:

Description:

VRD11/VRD10, K8 Rev F 2/3/4-Phase PWM Controllers with Integrated Dual MOSFET Drivers

Manufacturer:

Maxim Integrated Products

Datasheet:

Part Number:

Description:

Highly Integrated Level 2 SMBus Battery Chargers

Manufacturer:

Maxim Integrated Products

Datasheet:

Part Number:

Description:

Current Monitor and Accumulator with Integrated Sense Resistor; ; Temperature Range: -40°C to +85°C

Manufacturer:

Maxim Integrated Products

Part Number:

Description:

TSSOP 14/A�/RS-485 Transceivers with Integrated 100O/120O Termination Resis

Manufacturer:

Maxim Integrated Products

Part Number:

Description:

TSSOP 14/A�/RS-485 Transceivers with Integrated 100O/120O Termination Resis

Manufacturer:

Maxim Integrated Products

Part Number:

Description:

QFN 16/A�/AC-DC and DC-DC Peak-Current-Mode Converters with Integrated Step

Manufacturer:

Maxim Integrated Products

Part Number:

Description:

TDFN/A/65V, 1A, 600KHZ, SYNCHRONOUS STEP-DOWN REGULATOR WITH INTEGRATED SWI

Manufacturer:

Maxim Integrated Products

Part Number:

Description:

Integrated Temperature Controller f

Manufacturer:

Maxim Integrated Products

Part Number:

Description:

SOT23-6/I�/45MHz to 650MHz, Integrated IF VCOs with Differential Output

Manufacturer:

Maxim Integrated Products

Part Number:

Description:

SOT23-6/I�/45MHz to 650MHz, Integrated IF VCOs with Differential Output

Manufacturer:

Maxim Integrated Products

Part Number:

Description:

EVALUATION KIT/2.4GHZ TO 2.5GHZ 802.11G/B RF TRANSCEIVER WITH INTEGRATED PA

Manufacturer:

Maxim Integrated Products

Part Number:

Description:

QFN/E/DUAL PCIE/SATA HIGH SPEED SWITCH WITH INTEGRATED BIAS RESISTOR

Manufacturer:

Maxim Integrated Products

Datasheet: