ispPAC-CLK55xx Lattice Semiconductor, ispPAC-CLK55xx Datasheet - Page 34

ispPAC-CLK55xx

Manufacturer Part Number

ispPAC-CLK55xx

Description

In-System Programmable Clock Generator with Universal Fan-Out Buffer

Manufacturer

Lattice Semiconductor

Datasheet

1.ISPPAC-CLK55XX.pdf

(43 pages)

Lattice Semiconductor

type and version code (Figure 30). Access to the Identification Register is immediately available, via a TAP data

scan operation, after power-up of the device, or by issuing a Test-Logic-Reset instruction. The bit code for this

instruction is defined by Lattice as shown in Table 8.

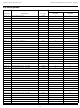

Figure 30. ispClock5500 Family ID Codes

In addition to the four instructions described above, there are 20 unique instructions specified by Lattice for the

ispClock5520. These instructions are primarily used to interface to the various user registers and the E

volatile memory. Additional instructions are used to control or monitor other features of the device, including bound-

ary scan operations. A brief description of each unique instruction is provided in detail below, and the bit codes are

found in Table 8.

PROGRAM_ENABLE – This instruction enables the ispClock5500’s programming mode.

PROGRAM_DISABLE – This instruction disables the ispClock5500’s programming mode.

BULK_ERASE – This instruction will erase all E

tronic security fuse (ESF). A bulk erase instruction must be issued before reprogramming a device. The device

must already be in programming mode for this instruction to execute.

ADDRESS_SHIFT – This instruction shifts address data into the address register (10 bits) in preparation for either

a PROGRAM or VERIFY instruction.

DATA_SHIFT – This instruction shifts data into or out of the data register (90 bits), and is used with both the PRO-

GRAM and VERIFY instructions.

PROGRAM – This instruction programs the contents of the data register to the E

to by the address register. The device must already be in programming mode for this instruction to execute.

PROG_INCR – This instruction first programs the contents of the data register into E

pointed to by the address register and then auto-increments the value of the address register. The device must

already be in programming mode for this instruction to execute.

PROGRAM_SECURITY – This instruction programs the electronic security fuse (ESF). This prevents data other

than the ID code and UES strings from being read fro the device. The electronic security fuse may only be reset by

issuing a BULK_ERASE command. The device must already be in programming mode for this instruction to exe-

cute.

E

E

2

2

Configured

Configured

Version

Version

(4 bits)

(4 bits)

0152h = ispClock5510

0150h = ispClock5520

MSB

MSB

(3.3V version)

(3.3V version)

Part Number

Part Number

XXXX / 0000 0001 0101 0010 / 0000 0100 001 / 1

XXXX / 0000 0001 0101 0000 / 0000 0100 001 / 1

(16 bits)

(16 bits)

2

CMOS bits in the device, including those the UES data and elec-

34

Lattice Semiconductor

Lattice Semiconductor

JEDEC Manufacturer

JEDEC Manufacturer

Identity Code for

Identity Code for

(11 bits)

(11 bits)

ispClock5500 Family Data Sheet

LSB

LSB

per 1149.1-1990

per 1149.1-1990

Constant ‘1’

Constant ‘1’

2

CMOS memory column pointed

(1 bit)

(1 bit)

2

CMOS memory column

2

CMOS non-