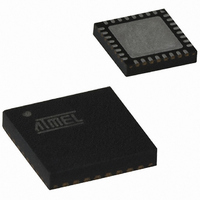

AT90PWM3-16MQ Atmel, AT90PWM3-16MQ Datasheet - Page 159

AT90PWM3-16MQ

Manufacturer Part Number

AT90PWM3-16MQ

Description

IC AVR MCU FLASH 8K 32QFN

Manufacturer

Atmel

Series

AVR® 90PWM Lightingr

Datasheet

1.AT90PWM3B-16SU.pdf

(361 pages)

Specifications of AT90PWM3-16MQ

Core Processor

AVR

Core Size

8-Bit

Speed

16MHz

Connectivity

SPI, UART/USART

Peripherals

Brown-out Detect/Reset, POR, PWM, WDT

Number Of I /o

27

Program Memory Size

8KB (8K x 8)

Program Memory Type

FLASH

Eeprom Size

512 x 8

Ram Size

512 x 8

Voltage - Supply (vcc/vdd)

2.7 V ~ 5.5 V

Data Converters

A/D 11x10b; D/A 1x10b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 105°C

Package / Case

32-QFN

Processor Series

AT90PWMx

Core

AVR8

Data Bus Width

8 bit

Data Ram Size

512 B

Interface Type

SPI, USART

Maximum Clock Frequency

16 MHz

Number Of Programmable I/os

27

Number Of Timers

2

Operating Supply Voltage

2.7 V to 5.5 V

Maximum Operating Temperature

+ 105 C

Mounting Style

SMD/SMT

3rd Party Development Tools

EWAVR, EWAVR-BL

Development Tools By Supplier

ATAVRDRAGON, ATSTK500, ATSTK600, ATAVRISP2, ATAVRONEKIT, ATAVRFBKIT, ATAVRISP2

Minimum Operating Temperature

- 40 C

On-chip Adc

10 bit, 11 Channel

On-chip Dac

10 bit, 1 Channel

For Use With

ATSTK600-SOIC - STK600 SOCKET/ADAPTER FOR SOICATAVRMC200 - KIT EVAL FOR AT90PWM3 ASYNCATAVRFBKIT - KIT DEMO BALLAST FOR AT90PWM2ATAVRISP2 - PROGRAMMER AVR IN SYSTEMATSTK520 - ADAPTER KIT FOR 90PWM

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

AT90PWM3-16MQT

Manufacturer:

Atmel

Quantity:

1 325

- Current page: 159 of 361

- Download datasheet (7Mb)

16.22.1

16.23 PSC Clock Sources

4317J–AVR–08/10

Fault events in Autorun mode

Note : Do not set the PARUNn bits on the three PSC at the same time.

Thanks to this feature, we can for example configure two PSC in slave mode (PARUNn = 1 /

PRUNn = 0) and one PSC in master mode (PARUNm = 0 / PRUNm = 0). This PSC master can

start all PSC at the same moment ( PRUNm = 1).

To complete this master/slave mechanism, fault event (input mode 7) is propagated from PSCn-

1 to PSCn and from PSCn to PSCn-1.

A PSC which propagate a Run signal to the following PSC stops this PSC when the Run signal

is deactivate.

According to the architecture of the PSC synchronization which build a “daisy-chain on the PSC

run signal” beetwen the three PSC, only the fault event (mode 7) which is able to “stop” the PSC

through the PRUN bits is transmited along this daisy-chain.

A PSC which receive its Run signal from the previous PSC transmits its fault signal (if enabled)

to this previous PSC. So a slave PSC propagates its fault events when they are configured and

enabled.

PSC must be able to generate high frequency with enhanced resolution.

Each PSC has two clock inputs:

•

•

Figure 16-39. Clock selection

PCLKSELn bit in PSC n Configuration register (PCNFn) is used to select the clock source.

PPREn1/0 bits in PSC n Control Register (PCTLn) are used to select the divide factor of the

clock.

CLK PLL from the PLL

CLK I/O

CLK

CLK

PLL

I/O

(1) : CK/16 for AT90PWM2/3

(2) : CK/64 for AT90PWM2/3

PCLKSELn

1

0

CK

PRESCALER

AT90PWM2/3/2B/3B

CLK

PSCn

PPREn1/0

159

Related parts for AT90PWM3-16MQ

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

IC AVR MCU FLASH 8K 32SOIC

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

MCU AVR 8K FLASH 16MHZ 32-QFN

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

DEV KIT FOR AVR/AVR32

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

INTERVAL AND WIPE/WASH WIPER CONTROL IC WITH DELAY

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

Low-Voltage Voice-Switched IC for Hands-Free Operation

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

MONOLITHIC INTEGRATED FEATUREPHONE CIRCUIT

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

AM-FM Receiver IC U4255BM-M

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

Monolithic Integrated Feature Phone Circuit

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

Multistandard Video-IF and Quasi Parallel Sound Processing

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

High-performance EE PLD

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

8-bit Flash Microcontroller

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

2-Wire Serial EEPROM

Manufacturer:

ATMEL Corporation

Datasheet: