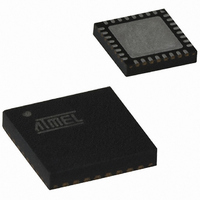

AT90PWM3-16MQ Atmel, AT90PWM3-16MQ Datasheet - Page 81

AT90PWM3-16MQ

Manufacturer Part Number

AT90PWM3-16MQ

Description

IC AVR MCU FLASH 8K 32QFN

Manufacturer

Atmel

Series

AVR® 90PWM Lightingr

Datasheet

1.AT90PWM3B-16SU.pdf

(361 pages)

Specifications of AT90PWM3-16MQ

Core Processor

AVR

Core Size

8-Bit

Speed

16MHz

Connectivity

SPI, UART/USART

Peripherals

Brown-out Detect/Reset, POR, PWM, WDT

Number Of I /o

27

Program Memory Size

8KB (8K x 8)

Program Memory Type

FLASH

Eeprom Size

512 x 8

Ram Size

512 x 8

Voltage - Supply (vcc/vdd)

2.7 V ~ 5.5 V

Data Converters

A/D 11x10b; D/A 1x10b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 105°C

Package / Case

32-QFN

Processor Series

AT90PWMx

Core

AVR8

Data Bus Width

8 bit

Data Ram Size

512 B

Interface Type

SPI, USART

Maximum Clock Frequency

16 MHz

Number Of Programmable I/os

27

Number Of Timers

2

Operating Supply Voltage

2.7 V to 5.5 V

Maximum Operating Temperature

+ 105 C

Mounting Style

SMD/SMT

3rd Party Development Tools

EWAVR, EWAVR-BL

Development Tools By Supplier

ATAVRDRAGON, ATSTK500, ATSTK600, ATAVRISP2, ATAVRONEKIT, ATAVRFBKIT, ATAVRISP2

Minimum Operating Temperature

- 40 C

On-chip Adc

10 bit, 11 Channel

On-chip Dac

10 bit, 1 Channel

For Use With

ATSTK600-SOIC - STK600 SOCKET/ADAPTER FOR SOICATAVRMC200 - KIT EVAL FOR AT90PWM3 ASYNCATAVRFBKIT - KIT DEMO BALLAST FOR AT90PWM2ATAVRISP2 - PROGRAMMER AVR IN SYSTEMATSTK520 - ADAPTER KIT FOR 90PWM

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

AT90PWM3-16MQT

Manufacturer:

Atmel

Quantity:

1 325

- Current page: 81 of 361

- Download datasheet (7Mb)

12.0.2

12.0.3

4317J–AVR–08/10

External Interrupt Mask Register – EIMSK

External Interrupt Flag Register – EIFR

Note:

• Bits 3..0 – INT3 – INT0: External Interrupt Request 3 - 0 Enable

When an INT3 – INT0 bit is written to one and the I-bit in the Status Register (SREG) is set

(one), the corresponding external pin interrupt is enabled. The Interrupt Sense Control bits in the

External Interrupt Control Register – EICRA – defines whether the external interrupt is activated

on rising or falling edge or level sensed. Activity on any of these pins will trigger an interrupt

request even if the pin is enabled as an output. This provides a way of generating a software

interrupt.

• Bits 3..0 – INTF3 - INTF0: External Interrupt Flags 3 - 0

When an edge or logic change on the INT3:0 pin triggers an interrupt request, INTF3:0 becomes

set (one). If the I-bit in SREG and the corresponding interrupt enable bit, INT3:0 in EIMSK, are

set (one), the MCU will jump to the interrupt vector. The flag is cleared when the interrupt routine

is executed. Alternatively, the flag can be cleared by writing a logical one to it. These flags are

always cleared when INT3:0 are configured as level interrupt.

Bit

Read/Write

Initial Value

Bit

Read/Write

Initial Value

1. n = 3, 2, 1 or 0.

When changing the ISCn1/ISCn0 bits, the interrupt must be disabled by clearing its Interrupt

Enable bit in the EIMSK Register. Otherwise an interrupt can occur when the bits are changed.

R/W

R/W

7

0

7

0

-

-

R/W

R/W

6

0

6

0

-

-

R/W

R/W

5

0

5

0

-

-

R/W

R/W

4

0

4

0

-

-

INTF3

INT3

R/W

R/W

3

0

3

0

AT90PWM2/3/2B/3B

INTF2

INT2

R/W

R/W

2

0

2

0

INTF1

INT1

R/W

R/W

1

0

1

0

IINTF0

IINT0

R/W

R/W

0

0

0

0

EIMSK

EIFR

81

Related parts for AT90PWM3-16MQ

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

IC AVR MCU FLASH 8K 32SOIC

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

MCU AVR 8K FLASH 16MHZ 32-QFN

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

DEV KIT FOR AVR/AVR32

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

INTERVAL AND WIPE/WASH WIPER CONTROL IC WITH DELAY

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

Low-Voltage Voice-Switched IC for Hands-Free Operation

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

MONOLITHIC INTEGRATED FEATUREPHONE CIRCUIT

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

AM-FM Receiver IC U4255BM-M

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

Monolithic Integrated Feature Phone Circuit

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

Multistandard Video-IF and Quasi Parallel Sound Processing

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

High-performance EE PLD

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

8-bit Flash Microcontroller

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

2-Wire Serial EEPROM

Manufacturer:

ATMEL Corporation

Datasheet: