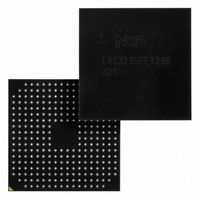

LPC3230FET296/01,5 NXP Semiconductors, LPC3230FET296/01,5 Datasheet

LPC3230FET296/01,5

Specifications of LPC3230FET296/01,5

935290764551

Available stocks

Related parts for LPC3230FET296/01,5

LPC3230FET296/01,5 Summary of contents

Page 1

ES_LPC3230 Errata sheet LPC3230 Rev. 8 — 1 February 2011 Document information Info Content Keywords LPC3230 errata Abstract This errata sheet describes both the known functional problems and any deviations from the electrical specifications known at the release date of ...

Page 2

... Added clarification regarding /01 Revision ‘A’ parts. • 5 20100205 The format of this errata sheet has been redesigned to comply with the new identity guidelines of NXP Semiconductors. • Added DDR write set-up time. Contact information For more information, please visit: For sales office addresses, please send an email to: ...

Page 3

... NXP Semiconductors 1. Product identification The LPC3230 devices typically have the following top-side marking: LPC3230FET296 xxxxxxx xxYYWWR The last letter in the last line (field ‘R’) will identify the device revision. This Errata Sheet covers the following revisions of the LPC3230: Table 1. Revision identifier (R) [1] ‘ ...

Page 4

... NXP Semiconductors Table 3. AC/DC deviations table AC/DC Short description deviations ESD.1 Weak ESD protection on Reset_N pin (pin M14) ES_LPC3230 Errata sheet Revision identifier ‘-’ All information provided in this document is subject to legal disclaimers. Rev. 8 — 1 February 2011 ES_LPC3230 Errata sheet LPC3230 Detailed description Section 4 ...

Page 5

... NXP Semiconductors 3. Functional problems detail 3.1 DMA.1: Single burst DMA memory-to-memory transfers have additional memory cycles when the DMA source memory is on the EMC bus Introduction: The DMA controller is an AHB master that can transfer blocks of data between peripheral-to-memory, memory-to-peripheral, peripheral-to-peripheral, and memory-to-memory ...

Page 6

... NXP Semiconductors DMA register values used in DMACConfig = 0x01 DMACCxSrcAddr = 0xe0000000; EMC_CS0 DMACCxDestAddr = 0xe0000040; EMC_CS0 DMACCxLLI = 0x0 DMACCxControl = 0x0c480004; Dest & Src addrs increment, Dest & Src 32-bit; Dburst & Sburst size 1; transfer size 4 DMACCxConfig = 0x01 EMCStaticConfig0 = 0x00000082; 32-bit width, Byte lane state 1 Fig 2 ...

Page 7

... NXP Semiconductors Work-around: When interfacing an external peripheral device that does not support burst mode access through the EMC Static Memory interface the following work-arounds are recommended: 1. Avoid using DMA to transfer read blocks of data from the external device. Instead use a software loop with LDR instruction to read blocks of data from the external device. ...

Page 8

... NXP Semiconductors Fig 3. 128 MB DDR SDRAM example 3.3 DDR.2: DDR EMC_D[15:0] to EMC_DQS[1:0] data output set-up time for MCU write to DDR provides limited timing margin su(Q) Remark: This affects both 1.8 V mobile and 2.5 V DDR SDRAM system implementations. Introduction: DDR memory interface signal EMC_DQS[1:0] is source synchronous, defined to be driven by the MCU center aligned to the data EMC_D[15:0] for writes, while driven by the DDR memory edge aligned to the EMC_D[15:0] for reads ...

Page 9

... NXP Semiconductors 2 inches of 50 Ω transmission line and 10 pF load capacitance. DDR memories specify EMC_D[15:0] to EMC_DQS[1:0] set-up time minimum as 400 ps. This leaves 200 ps set-up time margin due to customer specific load and PCB layout implementation. See the LPC3220_30_40_50 data sheet for the complete range of DDR data output set-up time, ...

Page 10

... NXP Semiconductors LPC32x0 EMC EMC_D[15:08] EMC_DQS1 EMC_DQM1 EMC_D[07:00] EMC_DQS0 EMC_DQM0 EMC_A[14:00] EMC_DYCS0_N EMC_Control EMC_CLK EMC_CLK_N EMC_CLKIN Fig 5. 128 MB DDR SDRAM example ES_LPC3230 Errata sheet DDR high byte (64M x 8) DQ7:0 22ohms DQS 22ohms DM BA1:0 / A12:0 nCS CKE, nRAS, nCAS, nWE CLK ...

Page 11

... NXP Semiconductors 3.4 DDR.1: DDR interface has >1.2 ns clock skew Introduction: DDR memory uses a differential clock which is generated by the LPC3230. The differential clock consists of two clock signals: EMC_CLK is the positive clock and DDR_nCLK is the negative clock. Problem: There is approximately 1. skew between the low transition of the DDR_nCLK and the high transition of the EMC_CLK ...

Page 12

... NXP Semiconductors 3.6 RTC.1: An RTC match doesn’t drive the ONSW pin active (HIGH) Introduction: An ONSW output pin (M15) is included in the LPC3230 to assist in waking up the chip after power is removed from all functions except the RTC and Battery RAM. When there is an active match condition the RTC will drive the ONSW pin HIGH. The RTC only drives ...

Page 13

... NXP Semiconductors 3.8 MCPWM.1: Input pins (MCI0-2) on the Motor Control PWM peripheral are not functional Introduction: On the LPC3230, the Motor Control PWM (MCPWM) peripheral is optimized for three-phase AC and DC motor control applications and can also be used in applications which require timing, counting, capture, and comparison. The MCPWM contains three input pins (MCI0-2) for PWM channels 0, 1, and 2 ...

Page 14

... NXP Semiconductors 3.9 HSUART.1: High speed UART receive FIFO and status can freeze Introduction: The three high speed UART's (HSUART) receive (RX) FIFOs can sometimes enter a state where they no longer accept received data. When this state occurs, the HSUART's RX FIFO will no longer accept data regardless of RX FIFO fill status. The receive state of the HSUART may indicate a number of possible, but invalid, receive statuses ...

Page 15

... NXP Semiconductors 4. AC/DC deviations detail 4.1 ESD.1: Weak ESD protection on Reset_N pad Introduction: The LPC3230 was designed to withstand electrostatic discharges up to 2000 V using the Human Body Model. Problem: The RESET_N pad (pin M14) does not pass ESD tests above 1000 V. Work-around: ...

Page 16

... In no event shall NXP Semiconductors be liable for any indirect, incidental, punitive, special or consequential damages (including - without limitation - lost profits, lost savings, business interruption, costs related to the removal or ...

Page 17

... NXP Semiconductors 6. Contents 1 Product identification . . . . . . . . . . . . . . . . . . . . 3 2 Errata overview . . . . . . . . . . . . . . . . . . . . . . . . . 3 3 Functional problems detail . . . . . . . . . . . . . . . . 5 3.1 DMA.1: Single burst DMA memory-to-memory transfers have additional memory cycles when the DMA source memory is on the EMC bus . . . . . 5 Introduction Problem Work-around 3.2 NOR.1: When booting from NOR flash, SDRAM devices will not release the data bus, preventing the LPC3230 from booting correctly ...