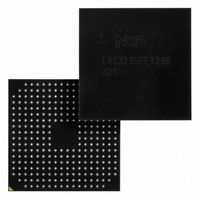

LPC3230FET296/01,5 NXP Semiconductors, LPC3230FET296/01,5 Datasheet - Page 14

LPC3230FET296/01,5

Manufacturer Part Number

LPC3230FET296/01,5

Description

IC ARM9 MCU 256K 296-TFBGA

Manufacturer

NXP Semiconductors

Series

LPC32x0r

Specifications of LPC3230FET296/01,5

Package / Case

296-TFBGA

Core Processor

ARM9

Core Size

16/32-Bit

Speed

266MHz

Connectivity

EBI/EMI, I²C, IrDA, Microwire, SPI, SSI, SSP, UART/USART, USB OTG

Peripherals

DMA, I²S, LCD, Motor Control PWM, PWM, WDT

Number Of I /o

51

Program Memory Type

ROMless

Ram Size

256K x 8

Voltage - Supply (vcc/vdd)

0.9 V ~ 3.6 V

Data Converters

A/D 3x10b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Processor Series

LPC32

Core

ARM926EJ-S

Data Bus Width

32 bit

Data Ram Size

256 KB

Interface Type

EMC

Maximum Clock Frequency

266 MHz

Number Of Timers

6

Operating Supply Voltage

1.31 V to 1.39 V

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

3rd Party Development Tools

MDK-ARM, RL-ARM, ULINK2

Minimum Operating Temperature

- 40 C

On-chip Adc

10 bit, 3 Channel

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Program Memory Size

-

Lead Free Status / Rohs Status

Lead free / RoHS Compliant

Other names

568-4964

935290764551

935290764551

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

LPC3230FET296/01,5

Manufacturer:

NXP Semiconductors

Quantity:

10 000

NXP Semiconductors

ES_LPC3230

Errata sheet

3.9 HSUART.1: High speed UART receive FIFO and status can freeze

Introduction:

The three high speed UART's (HSUART) receive (RX) FIFOs can sometimes enter a state

where they no longer accept received data. When this state occurs, the HSUART's RX

FIFO will no longer accept data regardless of RX FIFO fill status. The receive state of the

HSUART may indicate a number of possible, but invalid, receive statuses. These invalid

statuses may include RX FIFO or timeout interrupts pending with no receive data in the

RX FIFO, invalid RX FIFO status, stuck RX interrupts, or other possible RX statuses.

Once the HSUART enters this state, the state can only be cleared by a chip reset. This

applies to the U1_RX, U2_RX, and U7_RX pins. The HSUART's transmit side is not

affected by this issue and will work as normal when the HSUART receive side stops. The

four standard UARTs do not exhibit this behavior.

Problem:

It has been determined that this failed receive state can be entered by receiving a burst of

high frequency noise into the HSUART RX pin. High frequency noise consists of pulsed or

random toggling of the HSUART RX line at about 2.5 MHz or greater. The chance of the

HSUART entering the state increases with the number of pulses and frequency of the

pulses received. Generally, a single pulse won't cause the state to occur.

During normal data transfer with transfer rates 2400 bps (416 uS) to 921.6 Kbps

(1.085 uS), this state won't occur. However, conditions outside the transfer itself may

cause the state to occur. It has been observed in some systems that insertion of the serial

cable into the board's serial connector can cause connection noise or oscillations on the

transceiver. This noise is driven onto the HSUART RX pin from the transceiver as a series

of random pulses.

Work-around:

If all 7 UARTs aren't needed or 921.6 Kbps transfer rate isn't needed, use the standard

UARTs instead of the high speed UARTs to avoid the issue altogether. For systems that

require the HSUARTs, care must be taken to limit the exposure of the HSUART RX signal

for the type of signal conditions that can cause the state to occur. There are several

possible solutions that can help reduce the state from occurring.

Whenever the HSUART is not in use, place the HSUART into loopback mode. When in

loopback, the RX pin is connected internally to the HSUARTs TX pin and is isolated from

the external RX input. While in this loopback state, the condition won't occur on the

HSUART regardless of the signal on the RX input. The HSUART TX pin will remain in the

idle state in loopback mode when no data is being sent from the HSUART.

Optionally, if the HSUART is connected to a transceiver that supports enabling and

disabling of the input signal from the transceiver RX input to the transceiver RX output to

the HSUART RX input, disable it when not expecting a transmission. Regardless of how

the transceiver is connected to the RX pin, the RX pin should be prevented from floating at

power-up, reset, or when the transceiver is disabled. This can be done by adding a pull-up

resistor to the HSUART RX pin.

If using a system where the HSUART always need to be enabled, consider adding the

capability to sense when the cable has been plugged into the connector and switch the

HSUART out of loopback mode only once the cable has been installed to prevent cable

insertion noise.

All information provided in this document is subject to legal disclaimers.

Rev. 8 — 1 February 2011

ES_LPC3230

Errata sheet LPC3230

© NXP B.V. 2011. All rights reserved.

14 of 17