C8051F338-GM Silicon Laboratories Inc, C8051F338-GM Datasheet - Page 104

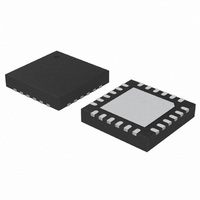

C8051F338-GM

Manufacturer Part Number

C8051F338-GM

Description

IC MCU 16K FLASH 24QFN

Manufacturer

Silicon Laboratories Inc

Series

C8051F33xr

Specifications of C8051F338-GM

Program Memory Type

FLASH

Program Memory Size

16KB (16K x 8)

Package / Case

24-QFN

Core Processor

8051

Core Size

8-Bit

Speed

25MHz

Connectivity

SMBus (2-Wire/I²C), SPI, UART/USART

Peripherals

POR, PWM, Temp Sensor, WDT

Number Of I /o

21

Ram Size

768 x 8

Voltage - Supply (vcc/vdd)

2.7 V ~ 3.6 V

Data Converters

A/D 16x10b; D/A 1x10b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Processor Series

C8051F3x

Core

8051

Data Bus Width

8 bit

Data Ram Size

768 B

Interface Type

I2C/SMBus/SPI/UART

Maximum Clock Frequency

25 MHz

Number Of Programmable I/os

21

Number Of Timers

4

Operating Supply Voltage

2.7 V to 3.6 V

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

3rd Party Development Tools

KSK-SL-TOOLSTICK, PK51, CA51, A51, ULINK2

Development Tools By Supplier

C8051F336DK

Minimum Operating Temperature

- 40 C

On-chip Adc

16-ch x 10-bit

On-chip Dac

1-ch x 10-bit

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Lead Free Status / Rohs Status

Lead free / RoHS Compliant

Other names

336-1427-5

- Current page: 104 of 226

- Download datasheet (2Mb)

C8051F336/7/8/9

17.5. Comparator0 Reset

Comparator0 can be configured as a reset source by writing a ‘1’ to the C0RSEF flag (RSTSRC.5).

Comparator0 should be enabled and allowed to settle prior to writing to C0RSEF to prevent any turn-on

chatter on the output from generating an unwanted reset. The Comparator0 reset is active-low: if the non-

inverting input voltage (on CP0+) is less than the inverting input voltage (on CP0-), the device is put into

the reset state. After a Comparator0 reset, the C0RSEF flag (RSTSRC.5) will read ‘1’ signifying

Comparator0 as the reset source; otherwise, this bit reads ‘0’. The state of the RST pin is unaffected by

this reset.

17.6. PCA Watchdog Timer Reset

The programmable Watchdog Timer (WDT) function of the Programmable Counter Array (PCA) can be

used to prevent software from running out of control during a system malfunction. The PCA WDT function

can be enabled or disabled by software as described in

page

prevents user software from updating the WDT, a reset is generated and the WDTRSF bit (RSTSRC.5) is

set to ‘1’. The state of the RST pin is unaffected by this reset.

17.7. Flash Error Reset

If a Flash read/write/erase or program read targets an illegal address, a system reset is generated. This

may occur due to any of the following:

The FERROR bit (RSTSRC.6) is set following a Flash error reset. The state of the RST pin is unaffected by

this reset.

17.8. Software Reset

Software may force a reset by writing a ‘1’ to the SWRSF bit (RSTSRC.4). The SWRSF bit will read ‘1’ fol-

lowing a software forced reset. The state of the RST pin is unaffected by this reset.

104

A Flash write or erase is attempted above user code space. This occurs when PSWE is set to ‘1’ and a

MOVX write operation targets an address above address 0x3DFF.

A Flash read is attempted above user code space. This occurs when a MOVC operation targets an

address above address 0x3DFF.

A Program read is attempted above user code space. This occurs when user code attempts to branch

to an address above 0x3DFF.

A Flash read, write or erase attempt is restricted due to a Flash security setting (see

“16.3. Security Options” on page

213; the WDT is enabled and clocked by SYSCLK / 12 following any reset. If a system malfunction

93).

Rev.1.0

Section “25.4. Watchdog Timer Mode” on

Section

Related parts for C8051F338-GM

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

SMD/C°/SINGLE-ENDED OUTPUT SILICON OSCILLATOR

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

Manufacturer:

Silicon Laboratories Inc

Datasheet:

Part Number:

Description:

N/A N/A/SI4010 AES KEYFOB DEMO WITH LCD RX

Manufacturer:

Silicon Laboratories Inc

Datasheet:

Part Number:

Description:

N/A N/A/SI4010 SIMPLIFIED KEY FOB DEMO WITH LED RX

Manufacturer:

Silicon Laboratories Inc

Datasheet:

Part Number:

Description:

N/A/-40 TO 85 OC/EZLINK MODULE; F930/4432 HIGH BAND (REV E/B1)

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

EZLink Module; F930/4432 Low Band (rev e/B1)

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4460 10 DBM RADIO TEST CARD 434 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4461 14 DBM RADIO TEST CARD 868 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4463 20 DBM RFSWITCH RADIO TEST CARD 460 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4463 20 DBM RADIO TEST CARD 868 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4463 27 DBM RADIO TEST CARD 868 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4463 SKYWORKS 30 DBM RADIO TEST CARD 915 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

N/A N/A/-40 TO 85 OC/4463 RFMD 30 DBM RADIO TEST CARD 915 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4463 20 DBM RADIO TEST CARD 169 MHZ

Manufacturer:

Silicon Laboratories Inc