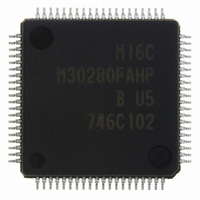

M30280FAHP#U5B Renesas Electronics America, M30280FAHP#U5B Datasheet

M30280FAHP#U5B

Specifications of M30280FAHP#U5B

Available stocks

Related parts for M30280FAHP#U5B

M30280FAHP#U5B Summary of contents

Page 1

REJ09B0047-0200 16 All information contained in these materials, including products and product specifications, represents information on the product at the time of publication and is subject to change by Renesas Technology Corp. without notice. Please review the latest information published ...

Page 2

This document is provided for reference purposes only so that Renesas customers may select the appropriate Renesas products for their use. Renesas neither makes warranties or representations with respect to the accuracy or completeness of the information contained in ...

Page 3

General Precautions in the Handling of MPU/MCU Products The following usage notes are applicable to all MPU/MCU products from Renesas. For detailed usage notes on the products covered by this manual, refer to the relevant sections of the manual. If ...

Page 4

How to Use This Manual 1. Purpose and Target Readers This manual is designed to provide the user with an understanding of the hardware functions and electrical characteristics of the MCU intended for users designing application systems incorporating ...

Page 5

Notation of Numbers and Symbols The notation conventions for register names, bit names, numbers, and symbols used in this manual are described below. (1) Register Names, Bit Names, and Pin Names Registers, bits, and pins are referred to in ...

Page 6

Register Notation The symbols and terms used in register diagrams are described below. XXX Register Bit Symbol XXX0 XXX1 XXX4 XXX5 XXX6 XXX7 *1 Blank: Set ...

Page 7

List of Abbreviations and Acronyms Abbreviation ACIA bps CRC DMA DMAC GSM Hi-Z IEBus I/O IrDA LSB MSB NC PLL PWM SFR SIM UART VCO All trademarks and registered trademarks are the property of their respective owners. IEBus is ...

Page 8

Quick Reference by Address ........................................................................... B-1 1. Overview ......................................................................................................... 1 1.1 Features ........................................................................................................................... 1 1.1.1 Applications ................................................................................................................ 1 1.1.2 Specifications ............................................................................................................. 2 1.2 Block Diagram .................................................................................................................. 4 1.3 Product Information .......................................................................................................... 6 1.4 Pin Assignment ............................................................................................................... 10 1.5 Pin Description ...

Page 9

Reset ..............................................................................................................32 5.1 Hardware Reset .............................................................................................................. 32 5.1.1 Hardware Reset 1 .................................................................................................... 32 5.1.2 Hardware Reset 2 .................................................................................................... 32 5.2 Software Reset ............................................................................................................... 33 5.3 Watchdog Timer Reset ................................................................................................... 33 5.4 Oscillation Stop Detection Reset .................................................................................... 33 5.5 Voltage ...

Page 10

Interrupts and Interrupt Vector ........................................................................................ 70 9.2.1 Fixed Vector Tables .................................................................................................. 70 9.2.2 Relocatable Vector Tables ........................................................................................ 71 9.3 Interrupt Control .............................................................................................................. 72 9.3.1 I Flag ........................................................................................................................ 75 9.3.2 IR Bit ........................................................................................................................ 75 9.3.3 ILVL2 to ILVL0 Bits and ...

Page 11

Timer B ...................................................................................................................... 114 12.2.1 Timer Mode ......................................................................................................... 116 12.2.2 Event Counter Mode ............................................................................................ 117 12.2.3 Pulse Period and Pulse Width Measurement Mode ............................................ 118 12.2.4 A/D Trigger Mode ................................................................................................ 120 12.3 Three-phase Motor Control Timer Function ................................................................ 122 ...

Page 12

Single Sweep Mode ............................................................................................ 227 15.1.4 Repeat Sweep Mode 0 ......................................................................................... 229 15.1.5 Repeat Sweep Mode 1 ......................................................................................... 231 15.1.6 Simultaneous Sample Sweep Mode .................................................................... 233 15.1.7 Delayed Trigger Mode 0 ....................................................................................... 236 15.1.8 Delayed Trigger Mode 1 ....................................................................................... ...

Page 13

Bits 4,5 : SDA/SCL Logic Output Value Monitor Bits SDAM/SCLM .................... 269 2 16.6.5 Bits 6 System Clock Select Bits ICK0, ICK1 ............................................ 269 16.6.6 Address Receive in STOP/WAIT Mode ............................................................... 269 2 16 ...

Page 14

CPU Rewrite Mode ..................................................................................................... 304 18.4.1 EW Mode 0 .......................................................................................................... 305 18.4.2 EW Mode 1 .......................................................................................................... 305 18.5 Register Description ................................................................................................... 306 18.5.1 Flash Memory Control Register 0 (FMR0) ........................................................... 306 18.5.2 Flash Memory Control Register 1 (FMR1) ........................................................... ...

Page 15

Precautions ............................................................................................... 350 20.1 SFR ............................................................................................................................ 350 20.1.1 For 80-Pin and 85-Pin Package ........................................................................... 350 20.1.2 For 64-Pin Package ............................................................................................. 350 22.1.3 Register Setting .................................................................................................... 350 20.1.4 For Flash Memory (128K+4K) Version and Mask ROM Version .......................... 351 20.2 ...

Page 16

Programmable I/O Ports ........................................................................................... 372 20.12 Electric Characteristic Differences Between Mask ROM and Flash Memory Version ... 373 20.13 Mask ROM Version ................................................................................................... 374 20.13.1 Internal ROM Area ............................................................................................. 374 20.13.2 Reserved Bit ....................................................................................................... 374 20.14 Flash Memory Version ...

Page 17

Quick Reference by Address Register Address 0000 16 0001 16 0002 16 0003 16 Processor mode register 0 0004 16 Processor mode register 1 0005 16 System clock control register 0 0006 16 System clock control register 1 0007 16 ...

Page 18

Quick Reference by Address Register Address 01B0 16 01B1 16 01B2 16 Flash memory control register 4 01B3 16 01B4 16 Flash memory control register 1 01B5 16 01B6 16 Flash memory control register 0 (2) 01B7 16 01B8 16 ...

Page 19

Quick Reference by Address Register Address 0340 16 0341 16 0342 16 Timer A1-1 register 0343 16 0344 16 Timer A2-1 register 0345 16 0346 16 Timer A4-1 register 0347 16 Three-phase PWM control register 0 0348 16 Three-phase PWM ...

Page 20

Quick Reference by Address Register Address 03C0 16 A/D register 0 03C1 16 03C2 16 A/D register 1 03C3 16 03C4 16 A/D register 2 03C5 16 03C6 16 A/D register 3 03C7 16 03C8 16 A/D register 4 03C9 ...

Page 21

M16C/28 Group (M16C/28, M16C/28B) SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER 1. Overview 1.1 Features The M16C/28 Group (M16C/28, M16C/28B) of single-chip control MCUs incorporates the M16C/60 series CPU core, employing the high-performance silicon gate CMOS technology and sophisticated instructions for a high ...

Page 22

1.1.2 Specifications Table 1.1 and 1.2 list specification outline. Table 1.1 Specifications (80/85-Pin Package) Item Function ...

Page 23

Table 1.2 Specifications (64-Pin Package) Item Function CPU Number of basic instructions Minimum instruction excution time ...

Page 24

1.2 Block Diagram Figure 1 block diagram of the M16C/28 Group, 80-pin and 85-pin ...

Page 25

I/O Ports Internal Peripheral Functions Timer (16 bits) Output (Timer Input (Timer B) ...

Page 26

1.3 Product Information Tables 1.3 and 1.4 list the M16C/28 Group product information and Figure 1.3 ...

Page 27

Part No ...

Page 28

Table 1.5 Product Code (Flash Memory Version) - M16C/28 Normal Version, 64-, 80-, and 85-Pin Packages ...

Page 29

(1) Flash Memory Version, PTLG0085JB-A (85F0G), Normal-ver. M30280FA B U5 XXXXXXX (2) Flash Memory Version, PLQP0080KB-A ...

Page 30

1.4 Pin Assignment Figures 1.5 to 1.7 show the pin Assignments (top view ...

Page 31

Table 1.8 Pin Characteristics for 85-Pin Package ...

Page 32

Table 1.8 Pin Characteristics for 85-Pin Package (continued ...

Page 33

/AN0 /AN0 /AN0 63 ...

Page 34

Table 1.9 Pin Characteristics for 80-Pin Package ...

Page 35

Table 1.9 Pin Characteristics for 80-Pin Package (continued ...

Page 36

/AN0 /AN0 /AN0 P10 ...

Page 37

Table 1.10 Pin Characteristics for 64-Pin Package ...

Page 38

Table 1.10 Pin Characteristics for 64-Pin Package (continued ...

Page 39

1.5 Pin Description Table 1.11 Pin Description (64-pin, 80-pin and 85-pin packages) Classification Symbol I/O Type ...

Page 40

Table 1.11 Pin Description (64-pin, 80-pin and 85-pin packages) (Continued) Classification Symbol I/O Type INPC1 to ...

Page 41

Table 1.11 Pin Description (80-pin and 85-pin packages only) (Continued) Classification Symbol I/O Type Serial I/O ...

Page 42

Central Processing Unit (CPU) Figure 2.1 shows the CPU registers. The register bank is comprised ...

Page 43

2.3 Frame Base Register (FB configured with 16 bits, and is used for FB ...

Page 44

Memory Figure 3 memory map of the M16C/28 Group. M16C/28 Group provides 1-Mbyte ...

Page 45

Special Function Register (SFR) SFR (Special Function Register) is the control register of peripheral functions. ...

Page 46

Table 4.2 SFR Information(2) Address 0040 16 0041 16 0042 16 0043 16 0044 INT3 interrupt ...

Page 47

Table 4.3 SFR Information(3) Address ~ ~ 01B0 16 01B1 16 01B2 16 01B3 Flash memory ...

Page 48

Table 4.4 SFR Information(4) Address 0300 TM, WG register 0 16 0301 16 0302 TM, WG ...

Page 49

Table 4.5 SFR Information(5) Address 0340 16 0341 16 0342 Timer A1-1 register 16 0343 16 ...

Page 50

Table 4.6 SFR Information(6) Address Count start flag 0380 16 Clock prescaler reset flag 0381 16 ...

Page 51

Table 4.7 SFR Information(7) Address 03C0 A/D register 0 16 03C1 16 03C2 A/D register 1 ...

Page 52

Reset Hardware reset, software reset, watchdog timer reset and oscillation stop detection reset are available ...

Page 53

RESET CC Figure 5.1 Example Reset Circuit 5.2 Software Reset When the PM03 bit in ...

Page 54

ROC td(P-R) More than td(ROC) RESET CPU clock Address Figure 5.2 Reset Sequence Table ...

Page 55

5.5 Voltage Detection Circuit Note V =5V is assumed in 5.5 Voltage Detection Circuit. CC The ...

Page 56

...

Page 57

Low Voltage Detection Interrupt Register ...

Page 58

5.5.1 Low Voltage Detection Interrupt If the D40 bit in the D4INT register is set to ...

Page 59

Low voltage detection circuit D4INT clock(the clock with which it VC27 operates also in wait mode) ...

Page 60

5.5.2 Limitations on Stop Mode The low voltage detection interrupt is immediately generated and the microcomputer ...

Page 61

Processor Mode The microcomputer supports single-chip mode only. Figures 6.1 and 6.2 show the associated ...

Page 62

Processeor Mode Register NOTES: 1. ...

Page 63

The internal bus consists of CPU bus, memory bus, and peripheral bus. Bus Interface Unit (BIU) ...

Page 64

Clock Generation Circuit The clock generation circuit contains four oscillator circuits as follows: (1) ...

Page 65

CM04 CM10=1(stop mode WAIT instruction R RESET Software reset NMI Interrupt ...

Page 66

System Clock Control Register Symbol 0 ...

Page 67

System Clock Control Register ...

Page 68

Oscillation Stop Detection Register NOTES: ...

Page 69

Peripheral Clock Select Register ...

Page 70

PLL Control Register ...

Page 71

The following describes the clocks generated by the clock generation circuit. 7.1 Main Clock The main ...

Page 72

7.2 Sub Clock The sub clock is generated by the sub clock oscillation circuit. This ...

Page 73

7.3 On-chip Oscillator Clock This clock is supplied by a variable on-chip oscillator. This clock is ...

Page 74

Set the CM07 bit to “0” (main clock), the CM17 to CM16 bits to “00 ...

Page 75

7.5 CPU Clock and Peripheral Function Clock The CPU clock is used to operate the CPU ...

Page 76

7.6 Power Control There are three power control modes. In this Chapter, all modes other ...

Page 77

7.6.1.6 On-chip Oscillator Mode The selected on-chip oscillator clock divided by 1 (undivided ...

Page 78

7.6.2.3 Pin Status During Wait Mode The I/O port pins retain their status held just ...

Page 79

7.6.3 Stop Mode In stop mode, all oscillator circuits are turned off, so are the CPU ...

Page 80

Figure 7.11 shows the state transition from normal operation mode to stop mode and wait ...

Page 81

Main clock oscillation PLL operation mode PLC07=1 High-speed mode CM11=1 CPU clock: f(PLL) (5) CPU clock: ...

Page 82

Table 7.5 Allowed Transition and Setting High-speed mode, middle-speed mode High-speed mode, 8 middle-speed mode ...

Page 83

7.7 System Clock Protective Function When the main clock is selected for the CPU clock source, ...

Page 84

7.8.1 Operation when CM27 bit is set to "0" (Oscillation Stop Detection Reset) When main ...

Page 85

7.8.3 How to Use Oscillation Stop and Re-oscillation Detect Function • The oscillation stop and re-oscillation ...

Page 86

Protection In the event that a program runs out of control, this function protects the ...

Page 87

Interrupts Note The SI/O4 interrupt of peripheral function interrupt is not available in the 64-pin ...

Page 88

9.1.1 Software Interrupts A software interrupt occurs when executing certain instructions. Software interrupts are non-maskable interrupts. ...

Page 89

9.1.2 Hardware Interrupts Hardware interrupts are classified into two types — special interrupts and peripheral function ...

Page 90

9.2 Interrupts and Interrupt Vector One interrupt vector consists of 4 bytes. Set the start address ...

Page 91

9.2.2 Relocatable Vector Tables The 256 bytes beginning with the start address set in the INTB ...

Page 92

9.3 Interrupt Control The following describes how to enable/disable the maskable interrupts, and how to set ...

Page 93

Interrupt Control Register NOTES: 1. This bit can ...

Page 94

Interrupt Request Cause Select Register NOTES: 1. When ...

Page 95

9.3.1 I Flag The I flag enables or disables the maskable interrupt. Setting the I flag ...

Page 96

9.4 Interrupt Sequence An interrupt sequence (the device behavior from the instant an interrupt is accepted ...

Page 97

9.4.1 Interrupt Response Time Figure 9.6 shows the interrupt response time. The interrupt response or interrupt ...

Page 98

9.4.3 Saving Registers In the interrupt sequence, the FLG register and PC are saved to the ...

Page 99

The operation of saving registers carried out in the interrupt sequence is dependent on whether the ...

Page 100

9.4.4 Returning from an Interrupt Routine The FLG register and PC in the state in which ...

Page 101

Priority level of each interrupt INT1 Timer B2 Timer B0 Timer A3 Timer A1 IC/OC interrupt ...

Page 102

______ 9.6 INT Interrupt _______ INTi interrupt (i triggered by the edges of ...

Page 103

______ 9.7 NMI Interrupt _______ An NMI interrupt request is generated when input on the NMI ...

Page 104

9.9 Address Match Interrupt An address match interrupt request is generated immediately before executing the instruction ...

Page 105

Address Match Interrupt Enable Register Address Match Interrupt ...

Page 106

10. Watchdog Timer The watchdog timer is the function that detects when a program is out ...

Page 107

Watchdog Timer Control Register Watchdog Timer ...

Page 108

11. DMAC Note Do not use SI/04 interrupt request as a DMA request in the 64-pin ...

Page 109

Table 11.1 DMAC Specifications Item No. of channels Transfer memory space Maximum No. of bytes transferred ...

Page 110

DMA0 Request Cause Select Register Bit Symbol NOTES: ...

Page 111

DMA1 Request Cause Select Register NOTES: 1. The causes ...

Page 112

DMAi Source Pointer ( (b19) (b16)(b15) (b23 NOTES: 1. ...

Page 113

11.1 Transfer Cycles The transfer cycle consists of a memory or SFR read (source read) bus ...

Page 114

(1) When the transfer unit bits and the source of transfer is ...

Page 115

11.2. DMA Transfer Cycles Any combination of even or odd transfer read and write adresses is ...

Page 116

11.3 DMA Enable When a data transfer starts after setting the DMAE bit in DMiCON register ...

Page 117

11.5 Channel Priority and DMA Transfer Timing If both DMA0 and DMA1 are enabled and DMA ...

Page 118

12. Timer Eight 16-bit timers, each capable of operating independently of the others, can be classified ...

Page 119

1/2 • Main clock f 1 • PLL clock • On-chip oscillator 1/8 clock f f ...

Page 120

12.1 Timer A Figure 12.3 shows a block diagram of the timer A. Figures 12.4 to ...

Page 121

Timer Ai Register ( (b15) (b8 NOTES: 1. The register ...

Page 122

One-shot Start Flag NOTES: 1. Make sure the ...

Page 123

12.1.1 Timer Mode In timer mode, the timer counts a count source generated internally (see Table ...

Page 124

12.1.2 Event Counter Mode In event counter mode, the timer counts pulses from an external device ...

Page 125

Timer Ai Mode Register (i (When not using two-phase pulse signal processing ...

Page 126

Table 12.3 Specifications in Event Counter Mode (when processing two-phase pulse signal with timers A2, A3 ...

Page 127

Timer Ai Mode Register (i (When using two-phase pulse signal processing ...

Page 128

12.1.2.1 Counter Initialization by Two-Phase Pulse Signal Processing This function initializes the timer count value to ...

Page 129

12.1.3 One-shot Timer Mode In one-shot timer mode, the timer is activated only once by one ...

Page 130

Timer Ai Mode Register (i ...

Page 131

12.1.4 Pulse Width Modulation (PWM) Mode In PWM mode, the timer outputs pulses of a given ...

Page 132

Timer Ai Mode Register ( ...

Page 133

Count source “H” Input signal to TA pin iIN “L” “H” PWM pulse output from TA ...

Page 134

12.2 Timer B Figure 12.15 shows a block diagram of the timer B. Figures 12.16 and ...

Page 135

Timer Bi Register (i (b15 (b8 NOTES: 1.The register must be ...

Page 136

12.2.1 Timer Mode In timer mode, the timer counts a count source generated internally (see Table ...

Page 137

12.2.2 Event Counter Mode In event counter mode, the timer counts pulses from an external device ...

Page 138

12.2.3 Pulse Period and Pulse Width Measurement Mode In pulse period and pulse width measurement mode, ...

Page 139

Count source “H” Measurement pulse “L” Reload register counter transfer timing Timing at which counter reaches ...

Page 140

12.2.4 A/D Trigger Mode A/D trigger mode is used together with simultaneous sample sweep mode or ...

Page 141

Timer Bi Mode Register ( NOTE: 1. ...

Page 142

12.3 Three-phase Motor Control Timer Function Timers A1, A2, A4 and B2 can be used ...

Page 143

Figure 12.25 Three-phase Motor Control Timer Functions Block Diagram page 123 ...

Page 144

Three-phase PWM Control Register Bit Symbol ...

Page 145

Three-phase PWM Control Register Bit ...

Page 146

Three-phase Output Buffer Register(i=0, Bit Symbol NOTES: 1. ...

Page 147

Timer Ai, Ai-1 Register (i= (b15) (b8 NOTES: 1. The ...

Page 148

Timer B2 Special Mode Register Symbol 0 ...

Page 149

(1) Timer B2 Register (b15) (b8 NOTE: 1. Access the register by ...

Page 150

Timer Ai Mode Register ...

Page 151

The three-phase motor control timer function is enabled by setting the INV02 bit in the ...

Page 152

Sawtooth Waveform as a Carrier Wave Sawtooth wave Signal wave Timer B2 Start trigger signal ...

Page 153

12.3.1 Position-Data-Retain Function This function is used to retain the position data synchronously with the ...

Page 154

12.3.1.2 Position-data-retain Function Control Register Figure 12.36 shows the structure of the position-data-retain function contol ...

Page 155

13. Timer S The Timer S (Input Capture/Output Compare : here after, Timer S is ...

Page 156

Figure 13.1 shows the block diagram of the IC/OC. Main clock, PLL clock, On-chip oscillator ...

Page 157

Figures 13.2 to 13.10 show registers associated with the IC/OC base timer, the time measurement ...

Page 158

Divider Register Base Timer Control Register 1 ...

Page 159

Base Timer Reset Register b15 b8 (b7) (b0 NOTES: 1. The G1BTRR register ...

Page 160

Time Measurement Control Register j (j ...

Page 161

Waveform Generation Register j (j b15 (b0 (b7) Waveform Generation ...

Page 162

Waveform Generation Register j (j b15 (b0 (b7) Figure 13.7 ...

Page 163

Function Select Register Function Enable Register b7 ...

Page 164

Interrupt Request Register NOTES: 1. When writing ...

Page 165

Interrupt Enable Register G1IE00 G1IE01 G1IE02 ...

Page 166

13.1 Base Timer The base timer is a free-running counter that counts an internally generated ...

Page 167

BCK1 to BCK0 Two-phase pulse input BTS bit ...

Page 168

State of a counter IT=1 in the G1BCR0 register (Base timer interrupt generated by the ...

Page 169

(1) When the base timer is reset while the base timer increments the counter P8 ...

Page 170

13.1.1 Base Timer Reset Register(G1BTRR) The G1BTRR register provides the capability to reset the base ...

Page 171

13.2 Interrupt Operation The IC/OC interrupt contains several request causes. Figure 13.18 shows the IC/OC ...

Page 172

13.4 Time Measurement Function In synchronization with an external trigger input, the value of the ...

Page 173

Table 13.6 Register Settings Associated with the Time Measurement Function Register Bit G1TMCRj CTS1 to ...

Page 174

When selecting the rising edge as a timer measurement trigger (a) (The CTS1 to CTS0 ...

Page 175

(a) With the prescaler function (When the G1TPRj register (j = 6,7) is set to ...

Page 176

13.5 Waveform Generating Function Waveforms are generated when the base timer value matches the G1POj ...

Page 177

13.5.1 Single-Phase Waveform Output Mode Output signal level of the OUTC1j pin becomes high("H") when ...

Page 178

(1) Free-running operation (The RST4, RST2, and RST1 bits in the G1BCR0 and G1BCR1 registers ...

Page 179

13.5.2 Phase-Delayed Waveform Output Mode Output signal level of the OUTC1j pin is inversed every ...

Page 180

(1) Free-running operation (The RST4, RST2, and RST1 bits in the G1BCR0 and G1BCR1 registers ...

Page 181

13.5.3 Set/Reset Waveform Output (SR Waveform Output) Mode Output signal level of the OUTC1j pin ...

Page 182

(1) Free-running operation (Bits RST2 and RST1 in the G1BCR0 register and the RST4 bit ...

Page 183

13.6 I/O Port Function Select The value in the G1FE and G1FS registers decides which ...

Page 184

13.6.1 INPC17 Alternate Input Pin Selection The input capture pin for IC/OC channel 7 can ...

Page 185

14. Serial I/O Note The SI/O4 interrupt of peripheral function interrupt is not available in the ...

Page 186

Main clock, PLL clock, or on-chip oscillator clock (UART0) RxD 0 Clock source selection CLK1 to ...

Page 187

PAR 1SP disabled STPS PAR RxDi STPS=1 2SP enabled 0 0 PAR STPS=1 enabled ...

Page 188

reverse IOPOL=0 RxD data RxD2 reverse circuit IOPOL=1 Reverse PAR 1SP disabled STPS ...

Page 189

UARTi Transmit Buffer Register (i (b15) (b8 NOTES: 1. Use MOV ...

Page 190

UARTi Transmit/receive Mode Register (i= Bit Symbol ...

Page 191

UARTi Transmit/receive Control Rregister 0 (i ...

Page 192

UARTi Transmit/receive Control Register 1 (i= Bit ...

Page 193

UART2 Special Mode Register Bit Symbol IICM ...

Page 194

UART2 Special Mode Register Symbol (b0) CKPH ...

Page 195

14.1.1 Clock Synchronous serial I/O Mode The clock synchronous serial I/O mode uses a transfer clock ...

Page 196

Table 14.2 Registers to Be Used and Settings in Clock Synchronous Serial I/O Mode Register Bit ...

Page 197

Table 14.3 lists pin functions for the case where the multiple transfer clock output pin select ...

Page 198

(1) Example of Transmit Timing (Internal clock is selected) Transfer clock “1” UiC1 register “0” Write ...

Page 199

14.1.1.1 Counter Measure for Communication Error Occurs If a communication error occurs while transmitting or receiving ...

Page 200

14.1.1.2 CLK Polarity Select Function Use the CKPOL bit in the UiC0 register (i ...