CY8C3866PVI-070 Cypress Semiconductor Corp, CY8C3866PVI-070 Datasheet - Page 111

CY8C3866PVI-070

Manufacturer Part Number

CY8C3866PVI-070

Description

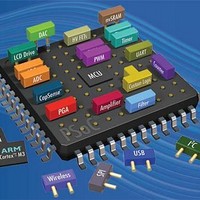

IC MCU 8BIT 64KB FLASH 48SSOP

Manufacturer

Cypress Semiconductor Corp

Series

PSOC™ 3 CY8C38xxr

Specifications of CY8C3866PVI-070

Package / Case

*

Voltage - Supply (vcc/vdd)

1.71 V ~ 5.5 V

Operating Temperature

-40°C ~ 85°C

Speed

67MHz

Number Of I /o

25

Eeprom Size

2K x 8

Core Processor

8051

Program Memory Type

FLASH

Ram Size

8K x 8

Program Memory Size

64KB (64K x 8)

Data Converters

A/D 2x20b, D/A 4x8b

Oscillator Type

Internal

Peripherals

CapSense, DMA, LCD, POR, PWM, WDT

Connectivity

CAN, EBI/EMI, I²C, LIN, SPI, UART/USART

Core Size

8-Bit

Operating Temperature (min)

-40C

Operating Temperature (max)

85C

Technology

CMOS

Processing Unit

Microcontroller

Operating Supply Voltage (min)

1.8V

Operating Supply Voltage (typ)

2.5/3.3/5V

Operating Supply Voltage (max)

5.5V

Package Type

SSOP

Screening Level

Industrial

Pin Count

48

Mounting

Surface Mount

Rad Hardened

No

Processor Series

CY8C38

Core

8051

Data Bus Width

32 bit

Data Ram Size

8 KB

Interface Type

I2C, SPI, UART, USB

Maximum Clock Frequency

67 MHz

Number Of Programmable I/os

28 to 72

Number Of Timers

4

Operating Supply Voltage

0.5 V to 5.5 V

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

Controller Family/series

(8051) PSOC 3

No. Of I/o's

25

Eeprom Memory Size

2KB

Ram Memory Size

8KB

Cpu Speed

67MHz

Rohs Compliant

Yes

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Lead Free Status / RoHS Status

Compliant, Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Part Number:

CY8C3866PVI-070

Manufacturer:

CYPRESS厂技术支持

Quantity:

20 000

11.5.5 SWD Interface

Table 11-76. SWD Interface AC Specifications

11.5.6 SWV Interface

Table 11-77. SWV Interface AC Specifications

Document Number: 001-11729 Rev. *R

f_SWDCK

T_SWDI_setup SWDIO input setup before SWDCK high T = 1/f_SWDCK max

T_SWDI_hold

T_SWDO_valid SWDCK high to SWDIO output

T_SWDO_hold SWDIO output hold after SWDCK low

Notes

51. Based on device characterization (Not production tested).

52. f_SWDCK must also be no more than 1/3 CPU clock frequency.

Parameter

Parameter

(PSoC 3 reading on SWDIO)

(PSoC 3 writing to SWDIO)

SWDCLK frequency

SWV mode SWV bit rate

SWDIO input hold after SWDCK high

SWDCK

SWDIO

SWDIO

Description

Description

T_SWDI_setup

Figure 11-72. SWD Interface Timing

[51]

[51]

T_SWDI_hold

3.3 V ≤ V

1.71 V ≤ V

1.71 V ≤ V

SWD over USBIO pins

T = 1/f_SWDCK max

T = 1/f_SWDCK max

T = 1/f_SWDCK max

DDD

DDD

DDD

Conditions

Conditions

≤ 5 V

< 3.3 V

< 3.3 V,

T_SWDO_valid

(1/f_SWDCK)

PSoC

Min

Min

T/4

T/4

T/4

–

®

–

–

–

T_SWDO_hold

–

3: CY8C38 Family

Typ

Typ

–

–

–

–

–

–

–

–

Data Sheet

5.5

14

2T/5

Max

7

Page 111 of 129

Max

[52]

33

–

–

–

[52]

[52]

Units

Units

MHz

MHz

MHz

Mbit

[+] Feedback