ADF4213BCP Analog Devices Inc, ADF4213BCP Datasheet - Page 16

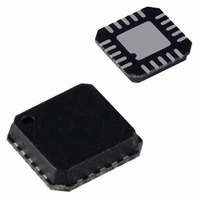

ADF4213BCP

Manufacturer Part Number

ADF4213BCP

Description

IC PLL FREQ SYNTHESIZER 20-LFCSP

Manufacturer

Analog Devices Inc

Type

Clock/Frequency Synthesizer (RF/IF)r

Datasheet

1.ADF4213BRU-REEL.pdf

(20 pages)

Specifications of ADF4213BCP

Rohs Status

RoHS non-compliant

Pll

Yes

Input

CMOS

Output

Clock

Number Of Circuits

1

Ratio - Input:output

3:1

Differential - Input:output

Yes/No

Frequency - Max

3GHz

Divider/multiplier

No/No

Voltage - Supply

2.7 V ~ 5.5 V

Operating Temperature

-40°C ~ 85°C

Mounting Type

Surface Mount

Package / Case

20-LFCSP

Frequency-max

3GHz

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Part Number:

ADF4213BCP

Manufacturer:

ADI/亚德诺

Quantity:

20 000

ADF4210/ADF4211/ADF4212/ADF4213

PROGRAM MODES

Table III and Table V show how to set up the Program Modes

in the ADF421x family. The following should be noted:

1. IF and RF Analog Lock Detect indicate when the PLL is in

2. The IF Counter Reset mode resets the R and AB counters in

3. The Fastlock mode uses MUXOUT to switch a second loop

IF Power-Down

It is possible to program the ADF421x family for either synchro-

nous or asynchronous power-down on either the IF or RF side.

Synchronous IF Power-Down

Programming a “1” to P7 of the ADF421x family will initiate a

power-down. If P2 of the ADF421x family has been set to “0”

(normal operation), a synchronous power-down is conducted.

The device will automatically put the charge pump into three-

state and then complete the power-down.

Asynchronous IF Power-Down

If P2 of the ADF421x family has been set to “1” (three-state the

IF charge pump), and P7 is subsequently set to “1,” an asyn-

chronous power-down is conducted. The device will go into

power-down on the rising edge of LE, which latches the “1” to

the IF power-down bit (P7).

Synchronous RF Power-Down

Programming a “1” to P16 of the ADF421x family will initiate a

power-down. If P10 of the ADF421x family has been set to “0”

(normal operation), a synchronous power-down is conducted. The

device will automatically put the charge pump into three-state

and then complete the power-down.

Asynchronous RF Power-Down

If P10 of the ADF421x family has been set to “1” (three-state

the RF charge pump), and P16 is subsequently set to “1,” an

asynchronous power-down is conducted. The device will go into

power down on the rising edge of LE, which latches the “1” to

the RF power-down bit (P16).

Activation of either synchronous or asynchronous power-down

forces the IF/RF loop’s R and AB dividers to their load state

conditions and the IF/RF input section is debiased to a high-

impedance state.

The REF

RF power-downs are set.

The input register and latches remain active and are capable of

loading and latching data during all the power-down modes.

The IF/RF section of the devices will return to normal powered

up operation immediately upon LE latching a “0” to the

appropriate power-down bit.

lock. When the loop is locked and either IF or RF Analog

Lock Detect is selected, the MUXOUT pin will show a logic

high with narrow low-going pulses. When the IF/RF Analog

Lock Detect is chosen, the locked condition is indicated only

when both IF and RF loops are locked.

the IF section and also puts the IF charge pump into three-

state. The RF Counter Reset mode resets the R and AB

counters in the RF section and also puts the RF charge

pump into three-state. The IF and RF Counter Reset mode

does both of the above. Upon removal of the reset bits, the

AB counter resumes counting in close alignment with the R

counter (maximum error is one prescaler output cycle).

filter damping resistor to ground during Fastlock operation.

Activation of Fastlock occurs whenever RF CP Gain in the

RF Reference counter is set to one.

IN

oscillator circuit is only disabled if both the IF and

IF SECTION

PROGRAMMABLE IF REFERENCE (R) COUNTER

If control bits C2, C1 are 0, 0, the data is transferred from the

input shift register to the 14-bit IFR counter. Table III shows

the input shift register data format for the IFR counter and the

divide ratios possible.

IF Phase Detector Polarity

P1 sets the IF Phase Detector Polarity. When the IF VCO char-

acteristics are positive this should be set to “1.” When they are

negative it should be set to “0.” See Table III.

IF Charge Pump Three-State

P2 puts the IF charge pump into three-state mode when pro-

grammed to a “1.” It should be set to “0” for normal operation.

See Table III.

IF PROGRAM MODES

Table III and Table V show how to set up the Program Modes

in the ADF421x family.

IF Charge Pump Currents

IFCP2, IFCP1, IFCP0 program current setting for the IF

charge pump. See Table III.

PROGRAMMABLE IF AB COUNTER

If control bits C2, C1 are 0, 1, the data in the input register is used

to program the IF AB counter. The N counter consists of a 6-bit

swallow counter (A counter) and 12-bit programmable counter

(B counter). Table IV shows the input register data format for

programming the IF AB counter and the possible divide ratios.

IF Prescaler Value

P5 and P6 in the IF A, B Counter Latch sets the IF prescaler

value. See Table IV.

IF Power-Down

Table III and Table V show the power-down bits in the

ADF421x family.

IF Fastlock

The IF CP Gain bit (P8) of the IF N register in the ADF421x

family is the Fastlock Enable Bit. Only when this is “1” is IF

Fastlock enabled. When Fastlock is enabled, the IF CP current

is set to its maximum value. Since the IF CP Gain bit is con-

tained in the IF N Counter, only one write is needed to both

program a new output frequency and also initiate Fastlock. To

come out of Fastlock, the IF CP Gain bit on the IF N register

must be set to “0.” See Table IV.

RF SECTION

PROGRAMMABLE RF REFERENCE (R) COUNTER

If control bits C2, C1 are 1, 0, the data is transferred from the

input shift register to the 14-bit RFR counter. Table V shows

the input shift register data format for the RFR counter and the

possible divide ratios.

RF Phase Detector Polarity

P9 sets the IF Phase Detector Polarity. When the RF VCO

characteristics are positive this should be set to “1.” When they

are negative it should be set to “0.” See Table V.

RF Charge Pump Three-State

P10 puts the RF charge pump into three-state mode when pro-

grammed to a “1.” It should be set to “0” for normal operation.

See Table V.