XC3SD1800A-4CSG484C Xilinx Inc, XC3SD1800A-4CSG484C Datasheet - Page 20

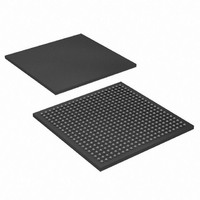

XC3SD1800A-4CSG484C

Manufacturer Part Number

XC3SD1800A-4CSG484C

Description

SPARTAN-3ADSP FPGA 1800K 484CSA

Manufacturer

Xilinx Inc

Series

Spartan™-3A DSPr

Datasheets

1.XC3S50A-4VQG100C.pdf

(7 pages)

2.XC3SD3400A-4FGG676C.pdf

(4 pages)

3.XC3SD3400A-4FGG676C.pdf

(101 pages)

Specifications of XC3SD1800A-4CSG484C

Total Ram Bits

1548288

Number Of Logic Elements/cells

37440

Number Of Labs/clbs

4160

Number Of I /o

309

Number Of Gates

1800000

Voltage - Supply

1.14 V ~ 1.26 V

Mounting Type

Surface Mount

Operating Temperature

0°C ~ 85°C

Package / Case

484-FBGA, CSPBGA

No. Of Logic Blocks

37440

No. Of Gates

1800000

No. Of Macrocells

37440

Family Type

Spartan-3A

No. Of Speed Grades

4

No. Of I/o's

309

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

For Use With

122-1574 - KIT DEVELOPMENT SPARTAN 3ADSP

Lead Free Status / RoHS Status

Lead free / RoHS Compliant, Lead free / RoHS Compliant

Other names

122-1537

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

XC3SD1800A-4CSG484C

Manufacturer:

XilinxInc

Quantity:

3 000

Part Number:

XC3SD1800A-4CSG484C

Manufacturer:

XILINX/赛灵思

Quantity:

20 000

I/O Timing

Pin-to-Pin Clock-to-Output Times

Table 17: Pin-to-Pin Clock-to-Output Times for the IOB Output Path

DS610 (v3.0) October 4, 2010

Product Specification

Notes:

1.

2.

3.

Clock-to-Output Times

T

The numbers in this table are tested using the methodology presented in

Table 7

This clock-to-output time requires adjustment whenever a signal standard other than LVCMOS25 is assigned to the Global Clock Input or a

standard other than LVCMOS25 with 12 mA drive and Fast slew rate is assigned to the data Output. If the former is true, add the appropriate

Input adjustment from

DCM output jitter is included in all measurements.

Symbol

ICKOFDCM

T

ICKOF

and

Table

When reading from the Output

Flip-Flop (OFF), the time from the

active transition on the Global

Clock pin to data appearing at the

Output pin. The DCM is in use.

When reading from OFF, the time

from the active transition on the

Global Clock pin to data appearing

at the Output pin. The DCM is not

in use.

10.

Table

Description

22. If the latter is true, add the appropriate Output adjustment from

LVCMOS25

output drive, Fast slew

rate, with DCM

LVCMOS25

output drive, Fast slew

rate, without DCM

Spartan-3A DSP FPGA Family: DC and Switching Characteristics

www.xilinx.com

Conditions

(2)

(2)

, 12 mA

, 12 mA

(3)

Table 26

and are based on the operating conditions set forth in

XC3SD1800A

XC3SD3400A

XC3SD1800A

XC3SD3400A

Device

Table

25.

Max

3.28

3.36

5.23

5.51

-5

Speed Grade

Max

3.51

3.82

5.58

6.13

-4

Units

ns

ns

ns

ns

20