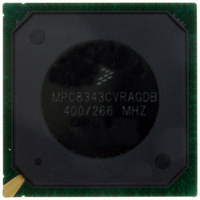

MPC8343CVRAGDB Freescale Semiconductor, MPC8343CVRAGDB Datasheet - Page 5

MPC8343CVRAGDB

Manufacturer Part Number

MPC8343CVRAGDB

Description

IC MPU PWRQUICC II 620-PBGA

Manufacturer

Freescale Semiconductor

Datasheet

1.MPC8343VRAGDB.pdf

(79 pages)

Specifications of MPC8343CVRAGDB

Processor Type

MPC83xx PowerQUICC II Pro 32-Bit

Speed

400MHz

Voltage

1.2V

Mounting Type

Surface Mount

Package / Case

620-PBGA

For Use With

CWH-PPC-8343N-VX - KIT EVAL SYSTEM QUICCSTART 8248CWH-PPC-8343N-VE - EVALUATION SYSTEM QUICC MPC8343E

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Features

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

MPC8343CVRAGDB

Manufacturer:

Freescale Semiconductor

Quantity:

10 000

Freescale Semiconductor

•

•

•

•

— Can operate as a stand-alone USB host controller

— External PHY with UTMI, serial and UTMI+ low-pin interface (ULPI)

Local bus controller (LBC)

— Multiplexed 32-bit address and data operating at up to 133 MHz

— Eight chip selects for eight external slaves

— Up to eight-beat burst transfers

— 32-, 16-, and 8-bit port sizes controlled by an on-chip memory controller

— Three protocol engines on a per chip select basis:

— Parity support

— Default boot ROM chip select with configurable bus width (8-, 16-, or 32-bit)

Programmable interrupt controller (PIC)

— Functional and programming compatibility with the MPC8260 interrupt controller

— Support for 8 external and 35 internal discrete interrupt sources

— Support for 1 external (optional) and 7 internal machine checkstop interrupt sources

— Programmable highest priority request

— Four groups of interrupts with programmable priority

— External and internal interrupts directed to host processor

— Redirects interrupts to external INTA pin in core disable mode.

— Unique vector number for each interrupt source

Dual industry-standard I

— Two-wire interface

— Multiple master support

— Master or slave I

— On-chip digital filtering rejects spikes on the bus

— System initialization data optionally loaded from I

DMA controller

— Four independent virtual channels

— Concurrent execution across multiple channels with programmable bandwidth control

— Handshaking (external control) signals for all channels: DMA_DREQ[0:3],

— All channels accessible to local core and remote PCI masters

– USB root hub with one downstream-facing port

– Enhanced host controller interface (EHCI) compatible

– High-speed (480 Mbps), full-speed (12 Mbps), and low-speed (1.5 Mbps) operations

– General-purpose chip select machine (GPCM)

– Three user-programmable machines (UPMs)

– Dedicated single data rate SDRAM controller

hardware

DMA_DACK[0:3], DMA_DDONE[0:3]

MPC8343EA PowerQUICC II Pro Integrated Host Processor Hardware Specifications, Rev. 10

2

C mode support

2

C interfaces

2

C-1 EPROM by boot sequencer embedded

Overview

5