MPC8560VT667LC Freescale Semiconductor, MPC8560VT667LC Datasheet - Page 18

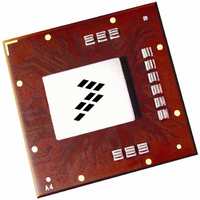

MPC8560VT667LC

Manufacturer Part Number

MPC8560VT667LC

Description

IC MPU POWERQUICC III 783-FCPBGA

Manufacturer

Freescale Semiconductor

Datasheet

1.MPC8560VT667LC.pdf

(36 pages)

Specifications of MPC8560VT667LC

Processor Type

MPC85xx PowerQUICC III 32-Bit

Speed

667MHz

Voltage

1.2V

Mounting Type

Surface Mount

Package / Case

783-FCPBGA

For Use With

MPC8560ADS-BGA - BOARD APPLICATION DEV 8560

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Features

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

MPC8560VT667LC

Manufacturer:

Freescale Semiconductor

Quantity:

10 000

Freescale Semiconductor, Inc.

Power Management

Power Management

The RapidIO unit on the MPC8560 supports the I/O and message-passing logical specifications, the

common transport specification, and the 8/16 LP-LVDS physical layer specification of the RapidIO

Interconnect Specification. It does not support the globally shared memory logical specification.

Highlights of the implementation include: support for four priority levels and ordering within a priority

level, CRC error management, 32- to 256-byte transactions and 8-bit data width ports.

The physical layer of the RapidIO unit can operate at up to 500 MHz. Because the interface is defined as a

source-synchronous, double-data-rate, LVDS-signaling interconnect, the theoretical unidirectional peak

bandwidth is 8 Gbps. Receive and transmit ports operate independently, resulting in an aggregate theoretical

bandwidth of 16 Gbps.

3.13.1 RapidIO Message Unit

The MPC8560’s RapidIO messaging supports one inbox/outbox structure for data and one doorbell

structure for messages. Both chaining and direct modes are provided for the outbox, and messages can hold

up to 16 packets of 256 bytes, or a total of 4 Kbytes.

3.14 Power Management

In addition to low-voltage operation and dynamic power management in its execution units, the MPC8560

supports four power consumption modes: full-on, doze, nap, and sleep. The three low-power modes: doze,

nap, and sleep, can be entered under software control in the e500 core or by external masters accessing a

configuration register.

Doze mode suspends execution of instructions in the e500 core. The core is left in a standby mode in which

cache snooping and time base interrupts are still enabled. Device logic external to the processor core is fully

functional in this mode.

Nap mode shuts down clocks to all the e500 functional units except the time base, which can be disabled

separately. No snooping is performed in nap mode, but the device logic external to the processor core is fully

functional.

Sleep mode shuts down not only the e500 core, but all of the MPC8560 I/O interfaces as well. Only the

interrupt controller and power management logic remain enabled so that the device can be awakened.

3.15 Clocking

The MPC8560 takes in the PCI_CLK/SYSCLK signal as an input to the device PLL and multiplies it by an

integer from 1 to 16 to generate the core complex bus clock (the platform clock), which operates at the same

frequency as the DDR DRAM data rate (for example, 266 or 333 MHz). The L2 cache also operates at this

frequency. The e500 core uses the CCB clock as an input to its PLL, which multiplies it again by 2, 2.5, 3,

or 3.5 to generate the core clock.

DLLs are used in the DDR SDRAM controller and the local bus memory controller (LBC) to generate

memory clocks. Six differential clock pairs are generated for DDR SDRAMs. Two clock outputs are

generated for the LBC.

The RapidIO transmit clock may be sourced from one of three locations: the platform clock, the RapidIO

receive clock, or a special differential clock input. This input is designed to receive inputs from an external

clock synthesis device driving a clock with a frequency of up to 500 MHz.

18

MPC8560 PowerQUICC III™

MOTOROLA

Integrated Communications Processor Product Brief

For More Information On This Product,

PRELIMINARY—SUBJECT TO CHANGE WITHOUT NOTICE

Go to: www.freescale.com