KSZ8893MBL Micrel Inc, KSZ8893MBL Datasheet - Page 98

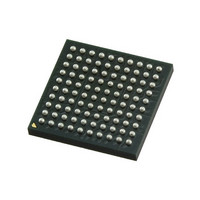

KSZ8893MBL

Manufacturer Part Number

KSZ8893MBL

Description

IC MANAGED SW 10/100 100-LFBGA

Manufacturer

Micrel Inc

Datasheet

1.KSZ8893MQL.pdf

(116 pages)

Specifications of KSZ8893MBL

Controller Type

Ethernet Switch Controller

Interface

MII, RMII, SNI

Voltage - Supply

3.1 V ~ 3.5 V

Operating Temperature

0°C ~ 70°C

Mounting Type

Surface Mount

Package / Case

100-LFBGA

Number Of Primary Switch Ports

3

Internal Memory Buffer Size

32

Operating Supply Voltage (typ)

3.3V

Fiber Support

Yes

Integrated Led Drivers

Yes

Power Supply Type

Analog/Digital

Data Rate (typ)

10/100Mbps

Vlan Support

Yes

Operating Temperature (max)

70C

Operating Temperature (min)

0C

Mounting

Surface Mount

Jtag Support

No

Operating Supply Voltage (max)

3.5V

Operating Supply Voltage (min)

3.1V

Operating Temperature Classification

Commercial

Data Rate

100Mbps

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

For Use With

576-1603 - EVAL KIT EXPERIMENTAL KSZ8893MQL

Current - Supply

-

Lead Free Status / RoHS Status

Compliant, Lead free / RoHS Compliant

Other names

576-3090

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

KSZ8893MBL

Manufacturer:

Micrel

Quantity:

1 272

Company:

Part Number:

KSZ8893MBLI

Manufacturer:

Micrel

Quantity:

2 022

Additional MIB Counter Information

“Per Port” MIB counters are designed as “read clear.” These counters will be cleared after they are read.

“All Port Dropped Packet” MIB counters are not cleared after they are accessed and do not indicate overflow or

validity; therefore, the application must keep track of overflow and valid conditions.

To read out all the counters, the best performance over the SPI bus is (160+3)*8*200 = 260ms, where there are

160 registers, 3 overheads, 8 clocks per access, at 5MHz. In the heaviest condition, the counters will overflow in 2

minutes. It is recommended that the software read all the counters at least every 30 seconds.

A high performance SPI master is also recommended to prevent counters overflow.

December 2007

2. MIB Counter Read (Read port 2 “Rx64Octets” Counter)

3. MIB Counter Read (Read “Port1 TX Drop Packets” Counter)

Then,

Then

Read reg. 128 (0x80), overflow bit [31]

Read reg. 129 (0x81), counter bits [23:16]

Read reg. 130 (0x82), counter bits [15:8]

Read reg. 131 (0x83), counter bits [7:0]

Write to reg. 121 (0x79) with 0x1c

Write to reg. 122 (0x7A) with 0x2e

Read reg. 128 (0x80), overflow bit [31]

Read reg. 129 (0x81), counter bits [23:16]

Read reg. 130 (0x82), counter bits [15:8]

Read reg. 131 (0x83), counter bits [7:0]

Write to reg. 121 (0x79) with 0x1d

Write to reg. 122 (0x7A) with 0x00

Read reg. 130 (0x82), counter bits [15:8]

Read reg. 131 (0x83), counter bits [7:0]

valid bit [30]

counter bits [29:24]

valid bit [30]

counter bits [29:24]

98

// Read MIB counter selected

// Trigger the read operation

// Read MIB counter selected

// Trigger the read operation

// If bit 31 = 1, there was a counter overflow

// If bit 30 = 0, restart (reread) from this register

// If bit 31 = 1, there was a counter overflow

// If bit 30 = 0, restart (reread) from this register

M9999-121007-1.5