HSC-ADC-EVALCZ Analog Devices Inc, HSC-ADC-EVALCZ Datasheet - Page 21

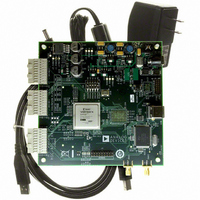

HSC-ADC-EVALCZ

Manufacturer Part Number

HSC-ADC-EVALCZ

Description

KIT EVAL ADC FIFO HI SPEED

Manufacturer

Analog Devices Inc

Datasheets

1.HSC-ADC-EVALB-DCZ.pdf

(28 pages)

2.HSC-ADC-EVALCZ.pdf

(32 pages)

3.HSC-ADC-EVALCZ.pdf

(40 pages)

Specifications of HSC-ADC-EVALCZ

Design Resources

EVALC PC Board Gerber File

Accessory Type

ADC Interface Board

Silicon Manufacturer

Analog Devices

Application Sub Type

ADC

Kit Application Type

Data Converter

Features

Buffer Memory Board For Capturing Digital Data, USB Port Interface, Windows 98, Windows 2000

Kit Contents

ADC Analyzer, Buffer Memory Board

Rohs Compliant

Yes

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

For Use With/related Products

Single ADC Version

Lead Free Status / Rohs Status

Supplier Unconfirmed

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

HSC-ADC-EVALCZ

Manufacturer:

Analog Devices Inc

Quantity:

135

Table 3. Serialized LVDS Tuning Controls

Control

Retune

Button

LVCMOS Tuning holds the controls related to tuning for the

LVCMOS port.

Table 4. LVCMOS Tuning Controls

Control

Delay

Load

Button

Debug

The Debug tab allows you to verify functionality of the DPG.

Frequency counter allows readback of the frequency counter

from the DPG to ensure correct operation.

Table 5. Frequency Counter Controls

Control

Port Selection

Frequency

Indicator

Go Button

Description

Manual trigger to retune the clock and data bits on

the serialized LVDS port. The alignment type is based

on the selected mode (aligned or centered). Tuning

is automatically performed when playback is started.

Description

Specifies the desired delay value. The value range is

from 0 to 1023 (0x3FF) in 10 ps units. This allows a

variation of approximately 10 ns.

A manual trigger to load the specified delay value

for the clock and data bits on the LVCMOS port.

Description

Selects the output port being used before

reading back the frequency

Displays the frequency read back from the DPG

Reads back the frequency counter from the DPG

Figure 45. Debug Tab

Rev. 0 | Page 21 of 40

Tx Config

The Tx Config tab holds controls for transmission features.

Idle Pattern specifies the transmit pattern when there is no

playback in progress. A four-sample pattern can be generated.

The four-sample values in the pattern are played sequentially,

then looped and played again until a vector file playback or the

feature is disabled.

Table 6. Idle Pattern Controls

Control

Enabled

Idle

Pattern

Text

Update

Button

PATTERN LIMITATIONS

The DPG is useful for playing a large range of user vector

patterns. However, there are a few basic limitations to the data.

•

•

•

FIFO4.x INTERFACE

The FIFO4.x interface component handles all interfacing

between the ADC capture board and the software package,

simply moving data from the hardware to the software data set

(vector). This interface exists for compatibility. The preferred

ADC interface is the ADC data capture component.

Additional information is available at www.analog.com/fifo.

The sample size of the output vector must be a multiple of

16 samples.

The minimum vector length is 640 samples.

The available memory in the DMM sockets limits the

maximum vector length. Each sample takes two bytes in

memory. Complex samples count as two samples in

memory.

Description

Enables/disables the idle pattern generation

feature. When the feature is disabled, zeros are

played on the output port.

Specifies the pattern values. When operating in dual

stream mode, four patterns must be specified for

each of the two streams. The values are played

sequentially from top to bottom.

Updates the idle pattern in the DPG.

Figure 46. Tx Config Tab

AN-905