HSC-ADC-EVALCZ Analog Devices Inc, HSC-ADC-EVALCZ Datasheet - Page 28

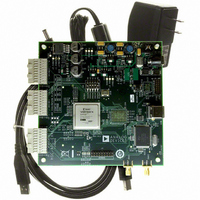

HSC-ADC-EVALCZ

Manufacturer Part Number

HSC-ADC-EVALCZ

Description

KIT EVAL ADC FIFO HI SPEED

Manufacturer

Analog Devices Inc

Datasheets

1.HSC-ADC-EVALB-DCZ.pdf

(28 pages)

2.HSC-ADC-EVALCZ.pdf

(32 pages)

3.HSC-ADC-EVALCZ.pdf

(40 pages)

Specifications of HSC-ADC-EVALCZ

Design Resources

EVALC PC Board Gerber File

Accessory Type

ADC Interface Board

Silicon Manufacturer

Analog Devices

Application Sub Type

ADC

Kit Application Type

Data Converter

Features

Buffer Memory Board For Capturing Digital Data, USB Port Interface, Windows 98, Windows 2000

Kit Contents

ADC Analyzer, Buffer Memory Board

Rohs Compliant

Yes

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

For Use With/related Products

Single ADC Version

Lead Free Status / Rohs Status

Supplier Unconfirmed

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

HSC-ADC-EVALCZ

Manufacturer:

Analog Devices Inc

Quantity:

135

AN-905

MIXER

Mixer performs a complex frequency shift of the input wave

form and produces real or complex waveform output. For

complex input, the complex output option is required. The

translation frequency may be positive or negative.

OUTPUT FORMATTER

Output Formatter converts normalized VisualAnalog data to

integer formats used by the DPG and the pattern saver.

Possible output formats include Gray Code, Unsigned Offset,

Two’s Complement, and Signed. Adjust the output bit

resolution and alignment as necessary.

PEAK HOLD

Peak Hold computes the peak data from the provided data. The

indicator on the component shows how many iterations have

occurred out of the total number of comparisons. To set the

total number of averages, click Settings. To reset the peak hold

series, click Reset.

The Peak Hold component is most efficient when running a

continuous update. A running peak hold occurs and the peak

hold continues until either the user stops the canvas or the

number of runs equals the terminal count. In the second case,

Peak Hold repeats another series of iterations unless a stop

block halts the canvas programmatically.

Figure 68. Output Formatter Settings Form

Figure 67. Mixer

Rev. 0 | Page 28 of 40

The Peak Hold component has two outputs. The top output

is the running peak FFT data. The second output is a numeric

value that indicates when the peak hold reaches its terminal

count by outputting a nonzero value.

A Stop component (see the Stop section) can use the terminal

value from the Peak Hold component to halt a continuous

update. In this case, when the Stop component receives a non

zero value and halts the canvas, the last update presents the final

peak hold.

Other components can use the terminal value as an indicator

to perform processing only on a nonzero value. See the Graph

section for more information on how to use the Graph compo

nent with this terminal value.

POWER/PHASE

Power/Phase converts data from an FFT into magnitude and

phase format. Click Power/Phase to open the options form,

allowing the formats to be set.

Figure 70. Power/Phase and Settings Form

Figure 69. Peak Hold Settings Form