KSZ8893MBL Micrel Inc, KSZ8893MBL Datasheet - Page 8

KSZ8893MBL

Manufacturer Part Number

KSZ8893MBL

Description

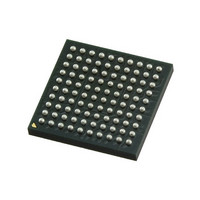

IC MANAGED SW 10/100 100-LFBGA

Manufacturer

Micrel Inc

Datasheet

1.KSZ8893MQL.pdf

(116 pages)

Specifications of KSZ8893MBL

Controller Type

Ethernet Switch Controller

Interface

MII, RMII, SNI

Voltage - Supply

3.1 V ~ 3.5 V

Operating Temperature

0°C ~ 70°C

Mounting Type

Surface Mount

Package / Case

100-LFBGA

Number Of Primary Switch Ports

3

Internal Memory Buffer Size

32

Operating Supply Voltage (typ)

3.3V

Fiber Support

Yes

Integrated Led Drivers

Yes

Power Supply Type

Analog/Digital

Data Rate (typ)

10/100Mbps

Vlan Support

Yes

Operating Temperature (max)

70C

Operating Temperature (min)

0C

Mounting

Surface Mount

Jtag Support

No

Operating Supply Voltage (max)

3.5V

Operating Supply Voltage (min)

3.1V

Operating Temperature Classification

Commercial

Data Rate

100Mbps

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

For Use With

576-1603 - EVAL KIT EXPERIMENTAL KSZ8893MQL

Current - Supply

-

Lead Free Status / RoHS Status

Compliant, Lead free / RoHS Compliant

Other names

576-3090

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

KSZ8893MBL

Manufacturer:

Micrel

Quantity:

1 272

Company:

Part Number:

KSZ8893MBLI

Manufacturer:

Micrel

Quantity:

2 022

Micrel, Inc.

KSZ8893MQL/MBL

List of Figures

Figure 1. Typical Straight Cable Connection........................................................................................................................................ 31

Figure 2. Typical Crossover Cable Connection.................................................................................................................................... 32

Figure 3. Auto-Negotiation and Parallel Operation .............................................................................................................................. 33

Figure 4. Destination Address Lookup Flow Chart, Stage 1 ................................................................................................................ 36

Figure 5. Destination Address Resolution Flow Chart, Stage 2 ........................................................................................................... 37

Figure 6. 802.1p Priority Field Format ................................................................................................................................................. 48

Figure 7. KSZ8893MQL/MBL EEPROM Configuration Timing Diagram .............................................................................................. 50

Figure 8. SPI Write Data Cycle............................................................................................................................................................ 52

Figure 9. SPI Read Data Cycle............................................................................................................................................................ 53

Figure 10. SPI Multiple Write ............................................................................................................................................................... 53

Figure 11. SPI Multiple Read............................................................................................................................................................... 53

Figure 12: Far-End Loopback Path...................................................................................................................................................... 54

Figure 13. Near-end (Remote) Loopback Path .................................................................................................................................... 55

Figure 14. EEPROM Interface Input Timing Diagram ........................................................................................................................ 102

Figure 15. EEPROM Interface Output Timing Diagram ..................................................................................................................... 102

Figure 16. SNI Input Timing Diagram ................................................................................................................................................. 103

Figure 17. SNI Output Timing Diagram.............................................................................................................................................. 103

Figure 18. MAC Mode MII Timing – Data Received from MII............................................................................................................. 104

Figure 19. MAC Mode MII Timing – Data Transmitted to MII ............................................................................................................. 104

Figure 20. PHY Mode MII Timing – Data Received from MII ............................................................................................................. 105

Figure 21. PHY Mode MII Timing – Data Transmitted to MII.............................................................................................................. 105

Figure 22: RMII Timing – Data Received from RMII .......................................................................................................................... 106

Figure 23: RMII Timing – Data Input to RMII ..................................................................................................................................... 106

Figure 24. I2C Input Timing ................................................................................................................................................................ 107

Figure 25. I2C Start Bit Timing ........................................................................................................................................................... 107

Figure 26. I2C Stop Bit Timing............................................................................................................................................................ 107

Figure 27. I2C Input Timing ................................................................................................................................................................ 107

Figure 28. SPI Input Timing ............................................................................................................................................................... 108

Figure 29. SPI Output Timing ............................................................................................................................................................ 109

Figure 30: Auto-Negotiation Timing ................................................................................................................................................... 110

Figure 31. Reset Timing .................................................................................................................................................................... 111

Figure 32. Recommended Reset Circuit............................................................................................................................................ 112

Figure 33. Recommended Reset Circuit for interfacing with CPU/FPGA Reset Output ..................................................................... 112

Figure 34. 128-Pin PQFP Package.................................................................................................................................................... 114

Figure 35. 100_Ball LFBGA Package ................................................................................................................................................. 115

December 2007

8

M9999-121007-1.5