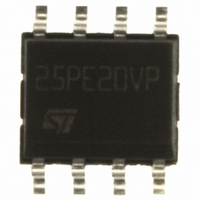

M25PE20-VMN6TP NUMONYX, M25PE20-VMN6TP Datasheet - Page 62

M25PE20-VMN6TP

Manufacturer Part Number

M25PE20-VMN6TP

Description

IC FLASH 2MBIT 75MHZ 8SOIC

Manufacturer

NUMONYX

Series

Forté™r

Datasheet

1.M25PE10-VMN6TP.pdf

(64 pages)

Specifications of M25PE20-VMN6TP

Format - Memory

FLASH

Memory Type

FLASH

Memory Size

2M (256K x 8)

Speed

75MHz

Interface

SPI, 3-Wire Serial

Voltage - Supply

2.7 V ~ 3.6 V

Operating Temperature

-40°C ~ 85°C

Package / Case

8-SOIC (3.9mm Width)

Cell Type

NOR

Density

2Mb

Access Time (max)

8ns

Interface Type

Serial (SPI)

Boot Type

Not Required

Address Bus

1b

Operating Supply Voltage (typ)

3.3V

Operating Temp Range

-40C to 85C

Package Type

SOIC N

Sync/async

Synchronous

Operating Temperature Classification

Industrial

Operating Supply Voltage (min)

2.7V

Operating Supply Voltage (max)

3.6V

Word Size

8b

Number Of Words

256K

Supply Current

8mA

Mounting

Surface Mount

Pin Count

8

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Other names

M25PE20-VMN6TPTR

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

M25PE20-VMN6TP

Manufacturer:

MICRON

Quantity:

3 000

Company:

Part Number:

M25PE20-VMN6TP

Manufacturer:

Numonyx

Quantity:

16 500

Part Number:

M25PE20-VMN6TP

Manufacturer:

MICRON/美光

Quantity:

20 000

Revision history

14

62/64

Revision history

Table 30.

07-Dec-2004

21-Dec-2004

25-Jan-2007

10-Jul-2006

6-Oct-2005

Date

Document revision history

Version

0.1

0.2

1.0

2

3

Document written

Notes 1 and 2 removed from

S08N silhouette corrected

Added

promoted to full Datasheet.

modify

to explain optimal use of Page Write and Page Program instructions. Clock

slew rate changed from 0.03 to 0.1 V/ns. Updated

information

Document converted to the new Numonyx template.

MLP package removed, SO8N package specifications updated (see

Section 12: Package

Figure 5: SPI modes supported

t

50 MHz frequency added. VFQFPN package added (see

Package

The sectors are further divided up into subsectors (see

memory organization

Important note on page 6

devices on the SPI bus

supply voltage

modified.

Reset conditions

At power-up the WIP bit is reset and the Lock Registers are reset (see

Section 7: Power-up and

V

M25PE20 and M25PE10 products processed in T9HX process added to

datasheet:

– WP pin replaces TSL (T7X technology), see

–

– subsector protection granularity removed in T9HX process, still exists in

–

– Status Register

Small text changes.

SHQZ

IO

(W) or Top Sector Lock (TSL)

Read Lock Register

Status Register

instructions added for T9HX process

T7X process

Table 5: M25PE20 memory organization

memory organization

max changed in

moved in

Table 22: AC characteristics (33 MHz

data,

mechanical).

Section 8: Reset

scheme. Added ECOPACK® information.

Page Write (PW)

and

Figure

and

(WRSR),

BP1, BP0 bits

V

Table 15: Absolute maximum

SS

mechanical).

and

Table 26: Timings after a Reset Low

(RDLR),

29.

updated and explanatory paragraph added.

ground

updated to show subsectors

power-down).

added.

Table 6: M25PE10 memory

on page

added, Reset timings table split into

An easy way to modify

SubSector Erase (SSE)

Table 29: Ordering information

and

Write to Lock Register

added.

updated and

Changes

and

Figure 4: Bus master and memory

Page Program (PP)

1.

SRWD bit

Section 4.8: Protection modes

and

operation). Document status

Note 2

Section 2.7: Write Protect

Table 6: M25PE10

added.

Table 29: Ordering

ratings.

data,

M25PE20, M25PE10

and

added. Timing line of

organization).

(WRLR),

Table 5: M25PE20

sections updated

A fast way to

Bulk Erase (BE)

Section 12:

pulse.

scheme.

Table 25:

Write

V

CC