ATXMEGA16A4-MH Atmel, ATXMEGA16A4-MH Datasheet - Page 56

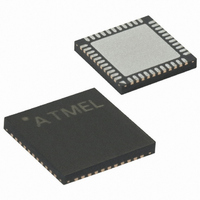

ATXMEGA16A4-MH

Manufacturer Part Number

ATXMEGA16A4-MH

Description

MCU AVR 16K FLASH 1.6V 44-QFN

Manufacturer

Atmel

Series

AVR® XMEGAr

Datasheet

1.ATXMEGA16A4-CUR.pdf

(108 pages)

Specifications of ATXMEGA16A4-MH

Core Processor

AVR

Core Size

8/16-Bit

Speed

32MHz

Connectivity

I²C, IrDA, SPI, UART/USART

Peripherals

Brown-out Detect/Reset, DMA, POR, PWM, WDT

Number Of I /o

34

Program Memory Size

16KB (8K x 16)

Program Memory Type

FLASH

Eeprom Size

1K x 8

Ram Size

2K x 8

Voltage - Supply (vcc/vdd)

1.6 V ~ 3.6 V

Data Converters

A/D 12x12b, D/A 2x12b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

44-VQFN Exposed Pad

Processor Series

ATXMEGA16x

Core

AVR8

Data Bus Width

8 bit, 16 bit

Data Ram Size

2 KB

Interface Type

I2C, SPI, USART

Maximum Clock Frequency

32 MHz

Number Of Programmable I/os

36

Number Of Timers

5

Operating Supply Voltage

1.6 V to 3.6 V

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

3rd Party Development Tools

EWAVR, EWAVR-BL

Development Tools By Supplier

ATAVRDRAGON, ATAVRISP2, ATAVRONEKIT

Minimum Operating Temperature

- 40 C

On-chip Adc

12 bit, 1 Channel

On-chip Dac

2 bit, 1 Channel

Package

44VFBGA EP

Device Core

AVR

Family Name

XMEGA

Maximum Speed

32 MHz

For Use With

ATAVRONEKIT - KIT AVR/AVR32 DEBUGGER/PROGRMMRATSTK600-TQFP44 - STK600 SOCKET/ADAPTER 44-TQFP770-1007 - ISP 4PORT ATMEL AVR MCU SPI/JTAG770-1004 - ISP 4PORT FOR ATMEL AVR MCU SPIATAVRISP2 - PROGRAMMER AVR IN SYSTEM

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Other names

ATXMEGA16A4-MU

ATXMEGA16A4-MU

ATXMEGA16A4-MU

8069Q–AVR–12/10

Mnemonics

LD

LDD

LD

LD

LD

LDD

STS

ST

ST

ST

ST

ST

ST

STD

ST

ST

ST

STD

LPM

LPM

LPM

ELPM

ELPM

ELPM

SPM

SPM

IN

OUT

PUSH

POP

LSL

LSR

Operands

Rd, -Y

Rd, Y+q

Rd, Z

Rd, Z+

Rd, -Z

Rd, Z+q

k, Rr

X, Rr

X+, Rr

-X, Rr

Y, Rr

Y+, Rr

-Y, Rr

Y+q, Rr

Z, Rr

Z+, Rr

-Z, Rr

Z+q,Rr

Rd, Z

Rd, Z+

Rd, Z

Rd, Z+

Z+

Rd, A

A, Rr

Rr

Rd

Rd

Rd

Description

Load Indirect and Pre-Decrement

Load Indirect with Displacement

Load Indirect

Load Indirect and Post-Increment

Load Indirect and Pre-Decrement

Load Indirect with Displacement

Store Direct to Data Space

Store Indirect

Store Indirect and Post-Increment

Store Indirect and Pre-Decrement

Store Indirect

Store Indirect and Post-Increment

Store Indirect and Pre-Decrement

Store Indirect with Displacement

Store Indirect

Store Indirect and Post-Increment

Store Indirect and Pre-Decrement

Store Indirect with Displacement

Load Program Memory

Load Program Memory

Load Program Memory and Post-Increment

Extended Load Program Memory

Extended Load Program Memory

Extended Load Program Memory and Post-

Increment

Store Program Memory

Store Program Memory and Post-Increment

by 2

In From I/O Location

Out To I/O Location

Push Register on Stack

Pop Register from Stack

Logical Shift Left

Logical Shift Right

Bit and Bit-test Instructions

(RAMPZ:Z)

(RAMPZ:Z)

Rd(n+1)

STACK

(Y + q)

(Z + q)

I/O(A)

Rd(0)

Rd(n)

Rd(7)

Operation

(X)

(X)

(X)

(Y)

(Y)

(Y)

Rd

Rd

Rd

Rd

Rd

Rd

(Z)

(Z)

R0

Rd

Rd

R0

Rd

Rd

Rd

Rd

(k)

C

C

Y

Z

Z

X

X

Y

Y

Z

Z

Z

Z

Z

←

←

←

←

←

←

←

←

←

←

←

←

←

←

←

←

←

←

←

←

←

←

←

←

←

←

←

←

←

←

←

←

←

←

←

←

←

←

←

←

←

←

←

←

←

←

←

Y - 1

(Y)

(Y + q)

(Z)

(Z),

Z+1

Z - 1,

(Z)

(Z + q)

Rd

Rr

Rr,

X + 1

X - 1,

Rr

Rr

Rr,

Y + 1

Y - 1,

Rr

Rr

Rr

Rr

Z + 1

Z - 1

Rr

(Z)

(Z)

(Z),

Z + 1

(RAMPZ:Z)

(RAMPZ:Z)

(RAMPZ:Z),

Z + 1

R1:R0

R1:R0,

Z + 2

I/O(A)

Rr

Rr

STACK

Rd(n),

0,

Rd(7)

Rd(n+1),

0,

Rd(0)

XMEGA A4

Flags

None

None

None

None

None

None

None

None

None

None

None

None

None

None

None

None

None

None

None

None

None

None

None

None

None

None

None

None

None

None

Z,C,N,V,H

Z,C,N,V

#Clocks

2

2

1

1

2

2

2

1

1

2

1

1

2

2

1

1

2

2

1

2

(1)(2)

(1)(2)

(1)(2)

(1)(2)

(1)(2)

(1)(2)

3

3

3

3

3

3

1

1

1

1

(1)

(1)

(1)

(1)

(1)

(1)

(1)

(1)

(1)

(1)

(1)

(1)

-

-

(1)

(1)

56