HD6417760BP200DQ Renesas Electronics America, HD6417760BP200DQ Datasheet - Page 196

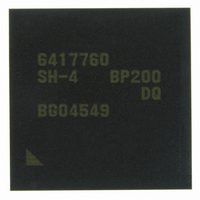

HD6417760BP200DQ

Manufacturer Part Number

HD6417760BP200DQ

Description

IC SUPERH MPU ROMLESS 256BGA

Manufacturer

Renesas Electronics America

Series

SuperH® SH7750r

Datasheet

1.D6417760BP200ADV.pdf

(1418 pages)

Specifications of HD6417760BP200DQ

Core Processor

SH-4

Core Size

32-Bit

Speed

200MHz

Connectivity

Audio Codec, CAN, EBI/EMI, FIFO, I²C, MFI, MMC, SCI, Serial Sound, SIM, SPI, USB

Peripherals

DMA, LCD, POR, WDT

Number Of I /o

69

Program Memory Type

ROMless

Ram Size

48K x 8

Voltage - Supply (vcc/vdd)

1.4 V ~ 1.6 V

Data Converters

A/D 4x10b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

256-BGA

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

Eeprom Size

-

Program Memory Size

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

HD6417760BP200DQ

Manufacturer:

Renesas Electronics America

Quantity:

10 000

- Current page: 196 of 1418

- Download datasheet (9Mb)

5.4

The following are additional notes on pipeline operation and the method of calculating the number

of clock cycles.

The number of states (CPU clock cycles) required for stages where an external bus access, etc.,

occurs may include an increased number of cycles, in addition to the number of memory access

cycles set by the bus state controller (BSC), etc.

For example, the occurrence of the following may result in idle cycles as observed from the

external bus.

1. Transfer of data from the logical address bus to the physical address bus

2. Transfer of data between buses using different operation clocks

The stages where external memory access occurs include some instruction fetch (I) and some

memory access (MA) stages.

Rev. 2.00 Feb. 12, 2010 Page 112 of 1330

REJ09B0554-0200

5. In the case of consecutive executions of MAC.W/MAC.L/MUL.L/MULS.W/MULU.W/

6. When an LDS to MACH/MACL is followed by an STS.L MACH/MACL, @-Rn

7. When an LDS to MACH/MACL is followed by MAC.W/MAC.L/MUL.L/MULS.W/

8. When an FSCHG or FRCHG instruction is followed by an LS group instruction that

9. When a single-precision FTRC instruction is followed by an STS FPUL, Rn instruction,

Usage Note

DMULS.L/DMULU.L, latency is decreased to 2 cycles.

instruction, latency of the LDS to MACH/MACL is 4 cycles.

MULU.W/DMULS.L/DMULU.L, latency of the LDS to MACH/MACL is 1 cycle.

reads from or writes to a floating-point register, the aforementioned LS group

instructions cannot be executed in parallel.

latency of the single-precision FTRC instruction is 1 cycle.

Related parts for HD6417760BP200DQ

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

KIT STARTER FOR M16C/29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/2D

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

R0K33062P STARTER KIT

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/23 E8A

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/25

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER H8S2456 SHARPE DSPLY

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C38C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C35C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8CL3AC+LCD APPS

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR RX610

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R32C/118

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV RSK-R8C/26-29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR SH7124

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR H8SX/1622

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV FOR SH7203

Manufacturer:

Renesas Electronics America

Datasheet: