HD6417760BP200DQ Renesas Electronics America, HD6417760BP200DQ Datasheet - Page 286

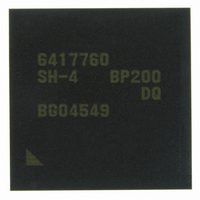

HD6417760BP200DQ

Manufacturer Part Number

HD6417760BP200DQ

Description

IC SUPERH MPU ROMLESS 256BGA

Manufacturer

Renesas Electronics America

Series

SuperH® SH7750r

Datasheet

1.D6417760BP200ADV.pdf

(1418 pages)

Specifications of HD6417760BP200DQ

Core Processor

SH-4

Core Size

32-Bit

Speed

200MHz

Connectivity

Audio Codec, CAN, EBI/EMI, FIFO, I²C, MFI, MMC, SCI, Serial Sound, SIM, SPI, USB

Peripherals

DMA, LCD, POR, WDT

Number Of I /o

69

Program Memory Type

ROMless

Ram Size

48K x 8

Voltage - Supply (vcc/vdd)

1.4 V ~ 1.6 V

Data Converters

A/D 4x10b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

256-BGA

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

Eeprom Size

-

Program Memory Size

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

HD6417760BP200DQ

Manufacturer:

Renesas Electronics America

Quantity:

10 000

- Current page: 286 of 1418

- Download datasheet (9Mb)

(3) Initial Page Write Exception

• Source: TLB is hit in a store access, but dirty bit D = 0

• Transition address: VBR + H'0000 0100

• Transition operations:

Rev. 2.00 Feb. 12, 2010 Page 202 of 1330

REJ09B0554-0200

Initial_write_exception()

{

}

The virtual address (32 bits) at which this exception occurred is set in TEA, and the

corresponding virtual page number (22 bits) is set in PTEH [31:10]. ASID in PTEH indicates

the ASID when this exception occurred.

The PC and SR contents for the instruction at which this exception occurred are saved in SPC

and SSR. The R15 contents at this time are saved in SGR.

Exception code H'080 is set in EXPEVT. The BL, MD, and RB bits are set to 1 in SR, and a

branch is made to PC = VBR + H'0100.

TEA = EXCEPTION_ADDRESS;

PTEH.VPN = PAGE_NUMBER;

SPC = PC;

SSR = SR;

SGR = R15;

EXPEVT = H'0000 0080;

SR.MD = 1;

SR.RB = 1;

SR.BL = 1;

PC = VBR + H'0000 0100;

Related parts for HD6417760BP200DQ

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

KIT STARTER FOR M16C/29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/2D

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

R0K33062P STARTER KIT

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/23 E8A

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/25

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER H8S2456 SHARPE DSPLY

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C38C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C35C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8CL3AC+LCD APPS

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR RX610

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R32C/118

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV RSK-R8C/26-29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR SH7124

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR H8SX/1622

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV FOR SH7203

Manufacturer:

Renesas Electronics America

Datasheet: