XR17D158CV-F Exar Corporation, XR17D158CV-F Datasheet - Page 71

XR17D158CV-F

Manufacturer Part Number

XR17D158CV-F

Description

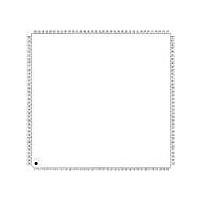

IC UART PCI BUS OCTAL 144LQFP

Manufacturer

Exar Corporation

Type

IrDA or RS- 485r

Datasheet

1.XR17D158CV-F.pdf

(73 pages)

Specifications of XR17D158CV-F

Number Of Channels

8

Package / Case

144-LQFP

Features

*

Fifo's

64 Byte

Protocol

RS485

Voltage - Supply

3.3V, 5V

With Auto Flow Control

Yes

With Irda Encoder/decoder

Yes

With False Start Bit Detection

Yes

With Modem Control

Yes

Mounting Type

Surface Mount

Data Rate

6.25 Mbps

Supply Voltage (max)

5.5 V

Supply Voltage (min)

4.5 V

Supply Current

5 mA

Maximum Operating Temperature

+ 70 C

Minimum Operating Temperature

0 C

Mounting Style

SMD/SMT

Operating Supply Voltage

5 V

No. Of Channels

8

Uart Features

Tx/Rx FIFO Counters

Supply Voltage Range

3V To 5.5V

Operating Temperature Range

0°C To +70°C

Digital Ic Case Style

LQFP

No. Of Pins

144

Rohs Compliant

Yes

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Lead Free Status / RoHS Status

Lead free / RoHS Compliant, Lead free / RoHS Compliant

Other names

1016-1291

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

XR17D158CV-F

Manufacturer:

Exar Corporation

Quantity:

10 000

Part Number:

XR17D158CV-F

Manufacturer:

EXAR/艾科嘉

Quantity:

20 000

xr

REV. 1.2.2

GENERAL DESCRIPTION................................................................................................. 1

PIN DESCRIPTIONS .......................................................................................................... 3

FUNCTIONAL DESCRIPTION ........................................................................................... 8

1.0 APPLICATION EXAMPLES .................................................................................................................. 9

2.0 XR17D158 REGISTERS ...................................................................................................................... 11

3.0 CRYSTAL OSCILLATOR / BUFFER ................................................................................................... 26

4.0 TRANSMIT AND RECEIVE DATA ...................................................................................................... 27

5.0 UART .................................................................................................................................................... 30

A

F

ORDERING INFORMATION

EATURES

PPLICATIONS

PCI Local Bus Interface............................................................................................................................................... 8

PCI Local Bus Configuration Space Registers ............................................................................................................ 8

EEPROM Interface ...................................................................................................................................................... 8

2.1 PCI LOCAL BUS CONFIGURATION SPACE REGISTERS .......................................................................... 11

2.2 DEVICE CONFIGURATION REGISTER SET ................................................................................................ 13

4.1 FIFO DATA LOADING AND UNLOADING THROUGH THE DEVICE CONFIGURATION REGISTERS IN 32-BIT

4.2 FIFO DATA LOADING AND UNLOADING THROUGH THE UART CHANNEL REGISTERS, THR AND RHR IN

5.1 PROGRAMMABLE BAUD RATE GENERATOR ........................................................................................... 30

5.2 TRANSMITTER ............................................................................................................................................... 31

F

F

T

F

F

F

T

T

T

T

F

T

T

F

T

F

F

F

T

F

T

F

IGURE

IGURE

ABLE

IGURE

IGURE

IGURE

ABLE

ABLE

ABLE

ABLE

IGURE

ABLE

ABLE

IGURE

ABLE

IGURE

IGURE

IGURE

ABLE

IGURE

ABLE

IGURE

2.2.1 THE INTERRUPT STATUS REGISTER ..................................................................................................................... 18

2.2.2 GENERAL PURPOSE 16-BIT TIMER/COUNTER [TIMERMSB, TIMELSB, TIMER, TIMECNTL] (DEFAULT 0XXX-XX-

2.2.3 8XMODE [7:0] (DEFAULT 0X00)................................................................................................................................ 21

2.2.4 REGA [15:8] RESERVED ........................................................................................................................................... 21

2.2.5 RESET [23:16] (DEFAULT 0X00)............................................................................................................................... 21

2.2.6 SLEEP [31:24] (DEFAULT 0X00) ............................................................................................................................... 22

2.2.7 DEVICE IDENTIFICATION AND REVISION............................................................................................................... 22

2.2.8 REGB REGISTER ....................................................................................................................................................... 23

2.2.9 MULTI-PURPOSE INPUTS AND OUTPUTS .............................................................................................................. 23

2.2.10 MPIO REGISTER ...................................................................................................................................................... 23

4.1.1 NORMAL RX FIFO DATA UNLOADING AT LOCATIONS 0X100, 0X300, 0X500, 0X700....................................... 27

4.1.2 SPECIAL RX FIFO DATA UNLOADING AT LOCATIONS 0X180, 0X380, 0X580, AND 0X780 .............................. 28

4.1.3 TX FIFO DATA LOADING AT LOCATIONS 0X100, 0X300, 0X500, 0X700, 0X900, 0XB00, 0XD00, 0XF00 .......... 28

5.2.1 TRANSMIT HOLDING REGISTER (THR) - WRITE-ONLY......................................................................................... 31

5.2.2 TRANSMITTER OPERATION IN NON-FIFO MODE .................................................................................................. 31

FORMAT. ....................................................................................................................................................... 27

8-BIT FORMAT. ............................................................................................................................................. 29

1: V

2: PCI L

3: XR17D158 D

4: D

5: D

6: UART C

7: UART C

8: TIMER CONTROL R

9: T

10: T

1. B

2. P

3. T

4. T

5. T

6. T

7. T

8. M

9. T

10. E

11. B

12. T

00-00) ............................................................................................................................................................................. 20

..................................................................................................................................................... 1

RANSMIT AND

ALID

EVICE

EVICE

LOCK

IN

YPICAL

YPICAL

HE

HE

IMER

YPICAL OSCILLATOR CONNECTIONS

YPICAL DATA RATES WITH A

ULTIPURPOSE INPUT

............................................................................................................................................... 1

RANSMITTER

XTERNAL

AUD

O

XR17D158 R

OCAL

G

C

UT OF THE

/C

LOBAL

C

C

OMBINATIONS OF

D

HANNEL

HANNEL

R

OUNTER CIRCUIT

ONFIGURATION

ONFIGURATION

A

A

IAGRAM

ATE

PPLICATION FOR A

PPLICATIONS IN AN

B

US

C

EVICE

I

G

NTERRUPT

LOCK

R

................................................................................................................................ 2

C

ENERATOR

O

ECEIVE

[7:0] I

[7:0] I

D

............................................................................................................................................................. 1

ONFIGURATION

PERATION IN NON

EVICE

EGISTER

C

C

ONFIGURATION

EGISTERS

/

ONNECTION FOR

NTERRUPT

NTERRUPT

OUTPUT INTERNAL CIRCUIT

D

R

R

.................................................................................................................................................. 2

VCC

............................................................................................................................................... 20

R

ATA

EGISTERS SHOWN IN

EGISTERS SHOWN IN

............................................................................................................................................. 30

EGISTER

S

U

14.7456 MH

ETS

E

R

AND

NIVERSAL

TABLE OF CONTENTS

...................................................................................................................................... 20

MBEDDED

EGISTER IN

S

S

C

.................................................................................................................................. 11

PACE

VIO S

OURCE

LEARING

-FIFO M

, INT0, INT1, INT2

............................................................................................................................... 26

R

EGISTERS

E

R

XTENDED

A

UPPLY

S

EGISTERS

E

Z CRYSTAL OR EXTERNAL CLOCK AT

DD

YSTEM

B

: .................................................................................................................. 19

NCODING

ODE

YTE FORMAT

-

IN

BYTE

DWORD

............................................................................................................. 14

V

............................................................................................................ 32

C

........................................................................................................... 24

OLTAGES

.......................................................................................................... 10

D

ARD

ATA

....................................................................................................... 12

..................................................................................................... 19

I

ALIGNMENT

.................................................................................................... 9

AND

R

ALIGNMENT

, 16C550

ATE

.............................................................................................. 9

INT3 .................................................................................. 19

........................................................................................ 26

................................................................................... 17

COMPATIBLE

.............................................................................. 17

16X S

............................................................ 29

AMPLING

5V PCI BUS OCTAL UART

........................................ 31

XR17D158