ADXL180WCPZ-RL Analog Devices Inc, ADXL180WCPZ-RL Datasheet - Page 17

ADXL180WCPZ-RL

Manufacturer Part Number

ADXL180WCPZ-RL

Description

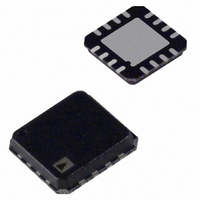

IC ACCELEROMETER CONFIG 16-LFCSP

Manufacturer

Analog Devices Inc

Series

iMEMS®r

Datasheet

1.ADXL180WCPZ-RL.pdf

(60 pages)

Specifications of ADXL180WCPZ-RL

Axis

X or Y

Acceleration Range

±50g, 100g, 150g, 200g, 250g, 350g, 500g

Voltage - Supply

5 V ~ 14.5 V

Output Type

Analog

Bandwidth

100Hz ~ 800Hz Selectable

Mounting Type

Surface Mount

Package / Case

16-LFQFN, CSP Exposed Pad

Package Type

LFCSP EP

Operating Supply Voltage (min)

5V

Operating Temperature (min)

-40C

Operating Temperature (max)

125C

Operating Temperature Classification

Automotive

Product Depth (mm)

5mm

Product Height (mm)

1.43mm

Product Length (mm)

5mm

Mounting

Surface Mount

Pin Count

16

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Sensitivity

-

Interface

-

Lead Free Status / Rohs Status

Compliant

Other names

ADXL180WCPZ-RLCT

0

1

SYNCHRONOUS COMMUNICATION

The ADXL180 data transmission can be synchronized to the

control module. This synchronization is accomplished by the

control module generating a synchronization pulse to the

ADXL180. The synchronization pulse is a voltage pulse that

is superimposed on the supply voltage by the center module.

Figure 14 shows the synchronization pulse timing. Upon detecting

a synchronization pulse, the ADXL180 transmits its data.

Configuring the ADXL180 for Synchronous Operation

Table 7. Sync Enable (SYEN) Options

SYEN

The user-defined SYEN bit determines whether the device is

used in synchronous operation or remains asynchronous.

SYEN, as shown in Table 7, must be set to SYEN = 1 to enable

synchronous operation.

Synchronization Pulse Detection

The ADXL180 uses a digital integration method to validate the

synchronization pulse. The ADXL180 detects the supply voltage

(V

circuit controls the count direction of an up-down counter. The

counter is clocked every 1 μs. The counter is incremented if the

ADXL180 detects a level exceeding V

mented if the ADXL180 detects a level below V

is not defined between these thresholds. If the synchronization

BP

) rising above the level of V

Synchronization pulse disabled. The device transmits

data every 228 μs based on the internal clock of the

device. Data is transmitted according to an internal state

machine sequence when powered on (default).

Synchronization pulse enabled. The device requires a

synchronization pulse to sample and transmit data. Data

transmission is in accordance with the internal state

machine of the device.

Definition

Figure 13. Asynchronous Point-To-Point Topology

MODULE

CENTER

SPT

V

BP

. The state of the level detection

SPT

V

DEVICE 1

BN

. The counter is decre-

V

NC

BN

SPND

V

NC

BC

. Operation

Rev. A | Page 17 of 60

pulse is fully below V

The counter saturates at zero. The synchronization pulse is con-

sidered valid on the next clock after the counter is incremented

to seven counts. The counter is gated off (blanked) after a valid

synchronization pulse is detected. Once the sync pulse has been

recognized as valid, a command is issued to start the acceleration

data analog-to-digital conversion. The ADC does not run conti-

nuously in synchronous mode.

The synchronization pulse detector is reenabled after t

is an idle bit transmission following the last data frame bit (see

the Data Frame Definition section). At this point, the device is

ready to receive the next sync pulse.

If the application requires or uses a pulse of nonuniform shape,

such as, for example, rising above V

toggling such that it falls below V

t

further information on application specific pulse recognition.

Note, this counter means that when an invalid length sync pulse

of less than seven counts is followed less than seven counts later

by a subsequent sync pulse, detection may occur when the

counter is incremented further by less than seven counts by the

second pulse.

Bus Discharge Enable

Table 8. Bus Discharge Enable

BDE

0

1

The bus discharge enable (BDE) bit in the configuration registers

can be set to aid in the discharge of the bus voltage after a syn-

chronization pulse is detected. If the BDE bit is set, the ADXL180

changes the bus current (I

synchronization pulse is detected. The control module then sets

the voltage on the bus to the nominal operating level. The bus

capacitance is discharged by the ADXL180 device. The current

level of I

voltage to the nominal supply voltage. The pull-down current

pulse can also be used as a handshake with the control module

acting as an acknowledgement of the synchronization pulse.

SPD

, consult Analog Devices, Inc., applications support for

Bus discharge disabled (default).

Bus discharge enabled. Only active when SYEN = 1.

Definition

SIG

acts as an active pull-down current to return the V

SPND

, the pulse is rejected and not detected.

BUS

) level from I

SPT

SPT

one or more times before

and subsequently

IDLE

to I

SIG

ADXL180

once a valid

B

, which

BP