SCC1300-D04 VTI Technologies, SCC1300-D04 Datasheet - Page 14

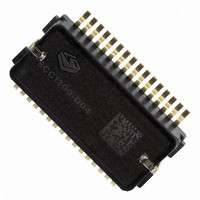

SCC1300-D04

Manufacturer Part Number

SCC1300-D04

Description

GYRO/ACC COMBO 3-AXIS +/-6G SPI

Manufacturer

VTI Technologies

Datasheet

1.SCC1300-D04_PWB.pdf

(30 pages)

Specifications of SCC1300-D04

Output Type

Digital - SPI

Sensor Type

Gyroscope and Accelerometer

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Other names

551-1069-2

4.2.2

VTI Technologies Oy

www.vti.fi

SPI Transfer Parity Mode

Figure 6. Communication example.

Each communication frame in the figure 6 contain 16 SCK cycles. After communication start

(CSN_G falling edge) the master sends ADR1 and performs a read access. In parallel the slave

sends Status Flags. During the transmission of the next data word (ADR2) the slave sends the

register value of ADR1 (Result_1). On ADR2 the master performs a write access (RW='1'). The

slave stores Data_2 in the register of ADR2 and sends the current register value of ADR2 to

MISO_G. After the transmission of data value during a write access the slave always sends Status

Flags. To receive Result_5 of the last read access the Master has to send an additional word ('Zero

Vector').

SCC1300 gyro ASIC is able to support parity check during SPI Transfer. This functionality is

controlled by the IC Identification Register. The internal parity status is reported in Status/Config

Register.

With parity enable bit set the SCC1300 gyro ASIC is expecting an additional parity bit after the

transmission of each 16 bit data word. This additional parity bit requires an additional SCK cycle,

i.e. the SPI frame consists of 17 SCK cycles instead of the normal 16 SCK cycles. Detecting a

wrong parity bit has the following consequences:

During read access:

The Parity Error Flag in the Status/Config Register is set. The SCC1300 reports the contents of the

received register address.

During write access:

The Parity Error Flag in the Status/Config Register is set. The SPI Write Access is cancelled.

These actions are performed either if the parity failure is detected in the address word or the data

word.

Due to the additional parity bit a single SPI Transfer is using now 17 Bit as shown in the Figure 7.

Figure 7. Communication in parity mode.

At the end of the data word the SPI master and the SPI slave have to add an additional parity bit.

Both devices have to check the received parity according to the selected parity mode odd or even.

Doc.Nr. 82 1131 00 A

Subject to changes

SCC1300-D04

Rev. 1.0

14/30