SCC1300-D04 VTI Technologies, SCC1300-D04 Datasheet - Page 18

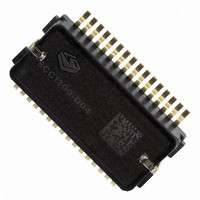

SCC1300-D04

Manufacturer Part Number

SCC1300-D04

Description

GYRO/ACC COMBO 3-AXIS +/-6G SPI

Manufacturer

VTI Technologies

Datasheet

1.SCC1300-D04_PWB.pdf

(30 pages)

Specifications of SCC1300-D04

Output Type

Digital - SPI

Sensor Type

Gyroscope and Accelerometer

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Other names

551-1069-2

4.4.2 MOSI data of SPI commands

Table 11. MOSI_A data during SPI read command

Table 12. MOSI_A data during write command

4.4.3 Error Conditioning

FRME-bit

PORST-bit

ST-bit

SAT-bit

VTI Technologies Oy

www.vti.fi

Register to be read

REVID

CTRL

STATUS

X_LSB

X_MSB

Y_LSB

Y_MSB

Z_LSB

Z_MSB

TEMP_LSB

TEMP_MSB

INT_STATUS

ID

Register to be written

RESET

RESET

RESET

CTRL

CTRL

CTRL

CTRL

While sending a frame, if CSB is raised to 1 before sending 16 SCKs, the frame is considered

invalid. The frame error is raised only if number of SCK pulses is not divisible by 8 to support

decremented mode reading. When an invalid frame is received, the last command is simply

ignored and the register contents are left unchanged. Status bit STATUS.FRME is set to indicate

this error condition. During next SPI frame error bit send out as bit number 2. Bit STATUS.FRME

will be reset, if correct frame is received.

PORST length is 1bit in SPI frame. PORST bit is set if chip is reset (HW reset by POR or supply

on/off) or under-voltage is detected. PORST bit is also set after power-up because chip has been in

reset state. PORST can be set to zero (reseted) by writing CTRL.PORST =0. Software (SW) reset

does not set PORST.

When CTRL.PORST bit is written to 0 via SPI, there is 300ns delay before register value is set to

zero.

Self-test frame status (ST) is set if STC or STS is alarmed or checksum is not passed.

Saturation status (SAT) is set if any of axis xyz is saturated and it can be cleared by INT_STATUS

register reading. This bit is kept active even failure condition is over if it is not acknowledged.

•

•

Function

Read ASIC revision ID

Read CTRL register

Read Status register

Read acceleration on X-axis, LSB

Read acceleration on X-axis, MSB

Read acceleration on Y-axis, LSB

Read acceleration on Y-axis, MSB

Read acceleration on Z-axis, LSB

Read acceleration on Z-axis, MSB

Read temperature, LSB

Read temperature, MSB

Read INT_STATUS register

Read product ID number

Reset component (data C'hex )

Reset component (data F'hex )

Function

Reset component (data 5'hex )

Set PORST to zero

Set chip to power down mode

Start self-diagnostic

Start memory self-test

CASE 1: Checksum fails and ST-frame bit is set 1. ST is set back to zero when (and only

if) new checksum calculation is passed.

CASE 2: ST-frame bit is set because STC or STS is alarmed. In this case ST-frame bit can

be cleared by INT_STATUS register reading.

Doc.Nr. 82 1131 00 A

Subject to changes

MOSI (15:0) [bits]

MOSI (15:0) [bits]

000000 01 xxxxxxxx

000001 00 xxxxxxxx

000010 00 xxxxxxxx

000100 00 xxxxxxxx

000101 01 xxxxxxxx

000110 01 xxxxxxxx

000111 00 xxxxxxxx

001000 00 xxxxxxxx

001001 01 xxxxxxxx

010010 01 xxxxxxxx

010011 00 xxxxxxxx

010110 00 xxxxxxxx

100111 01 xxxxxxxx

000011 10 00001100

000011 10 00000101

000011 10 00001111

000001 11 00000000

000001 11 00100000

000001 11 00001000

000001 11 00000100

MOSI [hex]

MOSI [hex]

1Cxx

4Cxx

9Dxx

01xx

04xx

08xx

10xx

15xx

19xx

20xx

25xx

49xx

58xx

0E0C

0E05

0E0F

0700

0720

0708

0704

SCC1300-D04

Rev. 1.0

18/30