KSZ8842-PMBL Micrel Inc, KSZ8842-PMBL Datasheet - Page 8

KSZ8842-PMBL

Manufacturer Part Number

KSZ8842-PMBL

Description

2-Port Ethernet Switch/Repeater + 32-bit/33MHz PCI Bus Interface ( )

Manufacturer

Micrel Inc

Datasheet

1.KSZ8842-PMBL.pdf

(119 pages)

Specifications of KSZ8842-PMBL

Controller Type

Ethernet Switch Controller

Interface

PCI

Voltage - Supply

3.1 V ~ 3.5 V

Operating Temperature

0°C ~ 70°C

Mounting Type

Surface Mount

Package / Case

100-LFBGA

Number Of Primary Switch Ports

2

Internal Memory Buffer Size

32

Operating Supply Voltage (typ)

3.3V

Fiber Support

Yes

Integrated Led Drivers

Yes

Phy/transceiver Interface

MII

Power Supply Type

Analog/Digital

Data Rate (typ)

10/100Mbps

Vlan Support

Yes

Operating Temperature (max)

70C

Operating Temperature (min)

0C

Mounting

Surface Mount

Jtag Support

No

Operating Supply Voltage (max)

3.5V

Operating Supply Voltage (min)

3.1V

Operating Temperature Classification

Commercial

Data Rate

100Mbps

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

For Use With

576-1636 - BOARD EVALUATION KSZ8842-PMQL

Current - Supply

-

Lead Free Status / RoHS Status

Supplier Unconfirmed, Lead free / RoHS Compliant

Other names

576-3089

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

KSZ8842-PMBL

Manufacturer:

TI

Quantity:

1 164

Company:

Part Number:

KSZ8842-PMBL AM

Manufacturer:

Micrel

Quantity:

1 053

Company:

Part Number:

KSZ8842-PMBL AM TR

Manufacturer:

Micrel Inc

Quantity:

10 000

Micrel, Inc.

KSZ8842-PMQL/PMBL

List of Figures

Figure 1. KSZ8842-PMQL/PMBL Functional Diagram ....................................................................................................... 1

Figure 2. KSZ8842-PMQL 128-Pin PQFP (Top View)........................................................................................................ 9

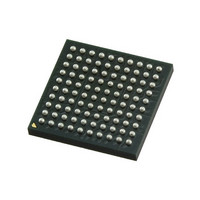

Figure 3. KSZ8842-PMBL 100-Ball LFBGA (Top View) .................................................................................................. 10

Figure 4. Typical Straight Cable Connection ................................................................................................................... 22

Figure 5. Typical Crossover Cable Connection ............................................................................................................... 23

Figure 6. Auto Negotiation and Parallel Operation .......................................................................................................... 24

Figure 7. Destination Address Lookup Flow Chart, Stage 1 ............................................................................................ 26

Figure 8. Destination Address Resolution Flow Chart, Stage 2....................................................................................... 27

Figure 9. 802.1p Priority Field Format.............................................................................................................................. 32

Figure 10. Port 2 Far-End Loop back Path ...................................................................................................................... 34

Figure 11. Port 1 and Port 2 Near-End (Remote) Loop back Path .................................................................................. 34

Figure 12. EEPROM Read Cycle Timing Diagram ........................................................................................................ 111

Figure 13. Auto-Negotiation Timing ............................................................................................................................... 112

Figure 14. Reset Timing ................................................................................................................................................. 113

Figure 15. Standard Package: 128-Pin PQFP ............................................................................................................... 115

Figure 16. Standard Package: 100-Ball LFBGA ............................................................................................................. 116

List of Tables

Table 1. KSZ8842-PMQL Pin Description......................................................................................................................... 15

Table 2. KSZ8842-PMBL Pin Description ......................................................................................................................... 19

Table 3. MDI/MDI-X Pin Definitions ................................................................................................................................. 22

Table 4. KSZ8841-PMQL/PMBL EEPROM Format......................................................................................................... 30

Table 5. FID+DA Lookup in VLAN Mode ......................................................................................................................... 31

Table 6. FID+SA Lookup in VLAN Mode ......................................................................................................................... 31

Table 7. EEPROM Format ............................................................................................................................................... 33

Table 8. Format of Per Port MIB Counters...................................................................................................................... 103

Table 9. Port 1s “Per Port” MIB Counters Indirect Memory Offsets............................................................................... 104

Table 10. “All Port Dropped Packet” MIB Counters Format............................................................................................ 104

Table 11. “All Port Dropped Packet” MIB Counters Indirect Memory Offsets................................................................. 104

Table 12. Static MAC Table Format (8 Entries) .............................................................................................................. 106

Table 13. Dynamic MAC Address Table Format (1024 Entries)..................................................................................... 107

Table 14. VLAN Table Format (16 Entries)..................................................................................................................... 108

Table 15. EEPROM Timing Parameters ........................................................................................................................ 111

Table 16. Auto Negotiation Parameters ......................................................................................................................... 112

Table 17. Reset Timing Parameters .............................................................................................................................. 113

Table 18. Transformer Selection Criteria ....................................................................................................................... 114

Table 19. Qualified Single Port Magnetics..................................................................................................................... 114

Table 20. Typical Reference Crystal Characteristics ...................................................................................................... 114

8

October 2007

M9999-100207-1.5