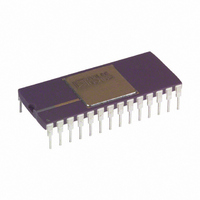

AD676BD Analog Devices Inc, AD676BD Datasheet - Page 10

AD676BD

Manufacturer Part Number

AD676BD

Description

ADC Single SAR 100KSPS 16-Bit Parallel 28-Pin SBCDIP

Manufacturer

Analog Devices Inc

Datasheet

1.AD676JNZ.pdf

(16 pages)

Specifications of AD676BD

Package

28SBCDIP

Resolution

16 Bit

Sampling Rate

100 KSPS

Architecture

SAR

Number Of Analog Inputs

1

Digital Interface Type

Parallel

Input Type

Voltage

Polarity Of Input Voltage

Bipolar

Rohs Status

RoHS non-compliant

Number Of Bits

16

Sampling Rate (per Second)

100k

Data Interface

Parallel

Number Of Converters

2

Power Dissipation (max)

480mW

Voltage Supply Source

Analog and Digital, Dual ±

Operating Temperature

-40°C ~ 85°C

Mounting Type

Through Hole

Package / Case

28-CDIP (0.600", 15.24mm)

For Use With

AD676-EB - BOARD EVAL SAMPLING ADC AD676

Lead Free Status / RoHS Status

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Part Number:

AD676BD

Manufacturer:

ADI/亚德诺

Quantity:

20 000

AD676

POWER SUPPLIES AND DECOUPLING

The AD676 has three power supply input pins. V

provide the supply voltages to operate the analog portions of the

AD676 including the ADC and sample-hold amplifier (SHA).

V

tions of the AD676 including the data output buffers and the

autocalibration controller.

As with most high performance linear circuits, changes in the

power supplies can produce undesired changes in the perfor-

mance of the circuit. Optimally, well regulated power supplies

with less than 1% ripple should be selected. The ac output im-

pedance of a power supply is a complex function of frequency,

and in general will increase with frequency. In other words, high

frequency switching such as that encountered with digital cir-

cuitry requires fast transient currents which most power supplies

cannot adequately provide. This results in voltage spikes on the

supplies. If these spikes exceed the 5% tolerance of the 12 V

supplies or the 10% limits of the +5 V supply, ADC perfor-

mance will degrade. Additionally, spikes at frequencies higher

than 100 kHz will also degrade performance. To compensate for

the finite ac output impedance of the supplies, it is necessary to

store “reserves” of charge in bypass capacitors. These capacitors

can effectively lower the ac impedance presented to the AD676

power inputs which in turn will significantly reduce the magni-

tude of the voltage spikes. For bypassing to be effective, certain

guidelines should be followed. Decoupling capacitors, typically

0.1 F, should be placed as closely as possible to each power

supply pin of the AD676. It is essential that these capacitors be

placed physically close to the IC to minimize the inductance of

the PCB trace between the capacitor and the supply pin. The

logic supply (V

the analog supplies (Vcc and V

erence input is also considered as a power supply pin in this re-

gard and the same decoupling procedures apply. These points

are displayed in Figure 4.

DD

provides the supply voltage which operates the digital por-

Figure 4. Grounding and Decoupling the AD676

+5V

0.1 F

DD

) should be decoupled to digital common and

18

V

COMMON

DD

SYSTEM

DIGITAL

DGND

11

COMMON

ANALOG

SYSTEM

EE

AGND

) to analog common. The ref-

13

AD676

0.1 F

0.1 F

12V –12V

V

12

CC

V

17

EE

0.1 F

CC

V

REF

11

and V

EE

–10–

Additionally, it is beneficial to have large capacitors (>47 F)

located at the point where the power connects to the PCB with

10 F capacitors located in the vicinity of the ADC to further

reduce low frequency ripple. In systems that will be subjected to

particularly harsh environmental noise, additional decoupling

may be necessary. RC-filtering on each power supply combined

with dedicated voltage regulation can substantially decrease

power supply ripple effects (this is further detailed in Figure 7).

BOARD LAYOUT

Designing with high resolution data converters requires careful

attention to board layout. Trace impedance is a significant issue.

A 1.22 mA current through a 0.5

drop of 0.6 mV, which is 4 LSBs at the 16-bit level for a 10 V

full-scale span. In addition to ground drops, inductive and ca-

pacitive coupling need to be considered, especially when high

accuracy analog signals share the same board with digital

signals.

Analog and digital signals should not share a common return

path. Each signal should have an appropriate analog or digital

return routed close to it. Using this approach, signal loops en-

close a small area, minimizing the inductive coupling of noise.

Wide PC tracks, large gauge wire, and ground planes are highly

recommended to provide low impedance signal paths. Separate

analog and digital ground planes are also desirable, with a single

interconnection point at the AD676 to minimize interference

between analog and digital circuitry. Analog signals should be

routed as far as possible from digital signals and should cross

them, if at all, only at right angles. A solid analog ground plane

around the AD676 will isolate it from large switching ground

currents. For these reasons, the use of wire wrap circuit con-

struction will not provide adequate performance; careful printed

circuit board construction is preferred.

GROUNDING

The AD676 has three grounding pins, designated ANALOG

GROUND (AGND), DIGITAL GROUND (DGND) and

ANALOG GROUND SENSE (AGND SENSE). The analog

ground pin is the “high quality” ground reference point for the

device, and should be connected to the analog common point in

the system.

AGND SENSE is intended to be connected to the input signal

ground reference point. This allows for slight differences in level

between the analog ground point in the system and the input

signal ground point. However no more than 100 mV is recom-

mended between the AGND and the AGND SENSE pins for

specified performance.

trace will develop a voltage

REV. A