MPC5200CBV400 Freescale Semiconductor, MPC5200CBV400 Datasheet - Page 20

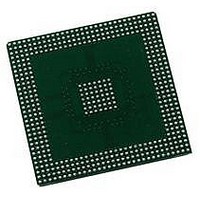

MPC5200CBV400

Manufacturer Part Number

MPC5200CBV400

Description

IC MPU 32BIT 400MHZ PPC 272-PBGA

Manufacturer

Freescale Semiconductor

Datasheet

1.MPC5200CVR400B.pdf

(80 pages)

Specifications of MPC5200CBV400

Processor Type

MPC52xx PowerPC 32-Bit

Speed

400MHz

Voltage

1.5V

Mounting Type

Surface Mount

Package / Case

272-PBGA

Core Size

32 Bit

No. Of I/o's

56

Ram Memory Size

16KB

Cpu Speed

400MHz

No. Of Timers

8

Embedded Interface Type

CAN, I2C, SPI, UART, USB

No. Of Pwm Channels

8

Digital Ic Case Style

BGA

Rohs Compliant

No

Family Name

MPC52xx

Device Core

PowerPC

Device Core Size

32b

Frequency (max)

400MHz

Instruction Set Architecture

RISC

Supply Voltage 1 (typ)

1.5V

Operating Supply Voltage (max)

1.58V

Operating Supply Voltage (min)

1.42V

Operating Temp Range

-40C to 85C

Operating Temperature Classification

Industrial

Mounting

Surface Mount

Pin Count

272

Package Type

BGA

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

Features

-

Lead Free Status / Rohs Status

Not Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

MPC5200CBV400

Manufacturer:

FREESCAL

Quantity:

200

Company:

Part Number:

MPC5200CBV400

Manufacturer:

Freescale Semiconductor

Quantity:

10 000

Company:

Part Number:

MPC5200CBV400B

Manufacturer:

FREESCAL

Quantity:

200

Electrical and Thermal Characteristics

3.3.5

3.3.5.1

3.3.5.2

In Standard SDRAM, all signals are activated on the Mem_clk from the Memory Controller and captured

on the Mem_clk clock at the memory device.

20

MBA (Bank Selects)

data

t

data

DQM (Data Mask)

DM

DM

mem_clk

Sym

t

t

valid

hold

Control Signals

valid

hold

setup

hold

MA (Address)

NOTE: Control Signals are composed of RAS, CAS, MEM_WE, MEM_CS, MEM_CS1 and CLK_EN

MDQ (Data)

MEM_CLK

SDRAM

MEM_CLK period

Control Signals, Address and MBA Valid after

rising edge of MEM_CLK

Control Signals, Address and MBA Hold after

rising edge of MEM_CLK

DQM valid after rising edge of MEM_CLK

DQM hold after rising edge of MEM_CLK

MDQ setup to rising edge of MEM_CLK

MDQ hold after rising edge of MEM_CLK

Memory Interface Timing-Standard SDRAM Read Command

Memory Interface Timing-Standard SDRAM Write Command

Figure 5. Timing Diagram—Standard SDRAM Memory Read Timing

t

t

t

valid

valid

valid

Description

Table 18. Standard SDRAM Memory Read Timing

Active

Row

t

hold

DM

valid

t

t

hold

hold

NOP

MPC5200 Data Sheet, Rev. 4

Column

READ

t

mem_clk

DM

t

mem_clk

NOP

data

hold

Min

7.5

0.2

—

—

—

*0.25-0.7

setup

*0.5

NOP

t

t

mem_clk

mem_clk

data

NOP

hold

Max

0.3

—

—

—

—

*0.25+0.4

*0.5+0.4

NOP

Freescale Semiconductor

Units

NOP

ns

ns

ns

ns

ns

ns

ns

SpecID

A5.1

A5.2

A5.3

A5.4

A5.5

A5.6

A5.7