PI7C9X7958ANBE Pericom Semiconductor, PI7C9X7958ANBE Datasheet - Page 25

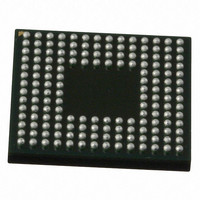

PI7C9X7958ANBE

Manufacturer Part Number

PI7C9X7958ANBE

Description

IC PCIE-TO-UART BRIDGE 160LFBGA

Manufacturer

Pericom Semiconductor

Specifications of PI7C9X7958ANBE

Applications

PCIe-to-Uart Bridge

Interface

Advanced Configuration Power Interface (ACPI)

Voltage - Supply

1.8V, 3.3V

Package / Case

160-LFBGA

Mounting Type

Surface Mount

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

PI7C9X7958ANBE

Manufacturer:

Pericom

Quantity:

152

11-0039

6.2.1.

6.2.2.

6.2.3.

March 2011 – Revision 1.4

Pericom Semiconductor

VENDOR ID REGISTER – OFFSET 00h

DEVICE ID REGISTER – OFFSET 00h

COMMAND REGISTER – OFFSET 04h

Other than the PCI 2.3 compatible configuration space header, the I/O bridge also implements

PCI express extended configuration space header, which includes advanced error reporting

registers. The following table details the allocation of the register fields of PCI express

extended capability space header. The first extended capability always begins at offset 100h

with a PCI Express Enhanced Capability header and the rest of capabilities are located at an

offset greater than 0FFh relative to the beginning of PCI compatible configuration space.

BIT

15:0

BIT

31:16

BIT

0

1

2

3

4

5

6

Next Capability

Offset = 000h

31 – 24

31 – 24

FUNCTION

Vendor ID

FUNCTION

Device ID

FUNCTION

I/O Space Enable

Memory Space

Enable

Bus Master Enable

Special Cycle

Enable

Memory Write And

Invalidate Enable

VGA Palette Snoop

Enable

Parity Error

Response Enable

Advanced Error Capabilities and Control Register

Capability Version

Uncorrectable Error Severity Register

Uncorrectable Error Status Register

Uncorrectable Error Mask Register

Correctable Error Status Register

Correctable Error Mask Register

23 – 16

23 – 16

Header Log Register

TYPE

TYPE

TYPE

RO

RW

RW

RW

RO

RO

RO

RO

RO

Reserved

Page 25 of 71

DESCRIPTION

Identifies Pericom as the vendor of this I/O bridge. The default

value may be changed by auto-loading from EEPROM.

Reset to 12D8h.

DESCRIPTION

Identifies this I/O bridge as the PI7C9X7958. The default value may

be changed by auto-loading from EEPROM.

Reset to 7958h.

DESCRIPTION

Controls a device’s response to I/O Space accesses. A value of 0

disables the device response. A value of 1 allows the device to

respond to I/O Space accesses.

Reset to 0b.

Controls a device’s response to Memory Space accesses. A value of 0

disables the device response. A value of 1 allows the device to

response to memory Space accesses.

Reset to 0b.

It is not implemented. Hardwired to 0b.

Does not apply to PCI Express. Must be hardwired to 0b.

Does not apply to PCI Express. Must be hardwired to 0b.

Does not apply to PCI Express. Must be hardwired to 0b.

Controls the device’s response to parity errors. When the bit is set,

the device must take its normal action when a parity error is

detected. When the bit is 0, the device sets its Detected Parity Error

Status bit when an error is detected.

PCI Express Extended Capability

15 – 8

15 – 8

ID = 001h

7 – 0

7 – 0

PCI Express® Octal UART

BYTE OFFSET

BYTE OFFSET

11Ch~128h

F4h - FCh

10Ch

100h

104h

108h

110h

114h

118h

PI7C9X7958

Datasheet