PI7C9X7958ANBE Pericom Semiconductor, PI7C9X7958ANBE Datasheet - Page 38

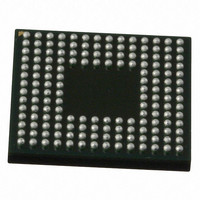

PI7C9X7958ANBE

Manufacturer Part Number

PI7C9X7958ANBE

Description

IC PCIE-TO-UART BRIDGE 160LFBGA

Manufacturer

Pericom Semiconductor

Specifications of PI7C9X7958ANBE

Applications

PCIe-to-Uart Bridge

Interface

Advanced Configuration Power Interface (ACPI)

Voltage - Supply

1.8V, 3.3V

Package / Case

160-LFBGA

Mounting Type

Surface Mount

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

PI7C9X7958ANBE

Manufacturer:

Pericom

Quantity:

152

11-0039

6.2.55. LINK STATUS REGISTER – OFFSET F0h

6.2.56. PCI EXPRESS ADVANCED ERROR REPORTING CAPABILITY ID REGISTER – OFFSET

6.2.57. CAPABILITY VERSION – OFFSET 100h

March 2011 – Revision 1.4

Pericom Semiconductor

100h

BIT

1:0

2

3

4

5

6

7

15:8

BIT

19:16

25:20

26

27

28

31:29

BIT

15:0

BIT

FUNCTION

Active State Power

Management

(ASPM) Control

Reserved

Read Completion

Boundary (RCB)

Link Disable

Retrain Link

Common Clock

Configuration

Extended Synch

RsvdP

FUNCTION

Extended

Capabilities ID

FUNCTION

FUNCTION

Link Speed

Negotiated Link

Width

Training Error

Link Training

Slot Clock

Configuration

Reserved

TYPE

TYPE

TYPE

TYPE

RW

RW

RW

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

RO

Page 38 of 71

DESCRIPTION

00b: ASPM is Disabled.

01b: L0s Entry Enabled.

10b: L1 Entry Enabled.

11b: L0s and L1 Entry Enabled.

Note that the receiver must be capable of entering L0s even when the

field is disabled.

Reset to 00b.

Reset to 0h.

It is not implemented. Hardwired to 0b.

It is not implemented. Hardwired to 0b.

It is not implemented. Hardwired to 0b.

0b: The components at both ends of a link are operating with

asynchronous reference clock.

1b: The components at both ends of a link are operating with a

distributed common reference clock.

Reset to 0b.

When set, it transmits 4096 FTS ordered sets in the L0s state for

entering L0 state and transmits 1024 TS1 ordered sets in the L1 state

for entering L0 state

Reset to 0b.

Reset to 00h.

DESCRIPTION

Read as 0001h to indicate that these are PCI express extended

capability registers for advance error reporting.

DESCRIPTION

DESCRIPTION

Indicates the negotiated Link Speed of the given PCIe Link.

Defined encodings are: 0001b, which indicates 2.5 Gb/s Link

Reset to 1h.

Indicates the negotiated width of the given PCIe Link,

Reset to 000001b.

When set, indicates a Link training error occurred.

This bit is cleared by hardware upon successful training of the link to

the L0 link state.

Reset to 0b.

When set, indicates the link training is in progress. Hardware clears

this bit once link training is complete.

Reset to 0b.

It is not implemented. Hardwired to 0b.

Reset to 000b.

PCI Express® Octal UART

PI7C9X7958

Datasheet