OM11024 NXP Semiconductors, OM11024 Datasheet - Page 21

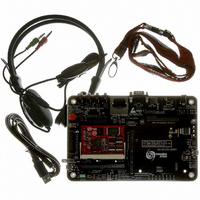

OM11024

Manufacturer Part Number

OM11024

Description

KIT EVAL FOR LPC313X

Manufacturer

NXP Semiconductors

Type

Microcontrollerr

Specifications of OM11024

Contents

2 Boards, cable and software

For Use With/related Products

LPC3131

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Other names

568-4719

- Current page: 21 of 72

- Download datasheet (402Kb)

NXP Semiconductors

LPC3130_3131

Preliminary data sheet

6.13 Multi-layer AHB

The following blocks can generate interrupts:

The multi-layer AHB is an interconnection scheme based on the AHB protocol that

enables parallel access paths between multiple masters and slaves in a system.

Multiple masters can have access to different slaves at the same time.

Figure 5

AHB masters and slaves are numbered according to their AHB port number.

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

Visibility of the interrupt’s request state before masking.

Support for nesting of interrupt service routines.

Interrupts routed to IRQ and to FIQ are vectored.

Level interrupt support.

NAND flash controller

USB 2.0 high-speed OTG

Event router

10-bit ADC

UART

LCD

MCI

SPI

I2C0 and I2C1 controllers

Timer0, Timer1, Timer2, and Timer3

I

I

DMA

2

2

S transmit: I2STX_0 and I2STX_1

S receive: I2SRX_0 and I2SRX_1

gives an overview of the multi-layer AHB configuration in the LPC3130/3131.

All information provided in this document is subject to legal disclaimers.

Rev. 1.04 — 27 May 2010

Low-cost, low-power ARM926EJ-S microcontrollers

LPC3130/3131

© NXP B.V. 2010. All rights reserved.

21 of 72

Related parts for OM11024

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

NXP Semiconductors designed the LPC2420/2460 microcontroller around a 16-bit/32-bitARM7TDMI-S CPU core with real-time debug interfaces that include both JTAG andembedded trace

Manufacturer:

NXP Semiconductors

Datasheet:

Part Number:

Description:

NXP Semiconductors designed the LPC2458 microcontroller around a 16-bit/32-bitARM7TDMI-S CPU core with real-time debug interfaces that include both JTAG andembedded trace

Manufacturer:

NXP Semiconductors

Datasheet:

Part Number:

Description:

NXP Semiconductors designed the LPC2468 microcontroller around a 16-bit/32-bitARM7TDMI-S CPU core with real-time debug interfaces that include both JTAG andembedded trace

Manufacturer:

NXP Semiconductors

Datasheet:

Part Number:

Description:

NXP Semiconductors designed the LPC2470 microcontroller, powered by theARM7TDMI-S core, to be a highly integrated microcontroller for a wide range ofapplications that require advanced communications and high quality graphic displays

Manufacturer:

NXP Semiconductors

Datasheet:

Part Number:

Description:

NXP Semiconductors designed the LPC2478 microcontroller, powered by theARM7TDMI-S core, to be a highly integrated microcontroller for a wide range ofapplications that require advanced communications and high quality graphic displays

Manufacturer:

NXP Semiconductors

Datasheet:

Part Number:

Description:

The Philips Semiconductors XA (eXtended Architecture) family of 16-bit single-chip microcontrollers is powerful enough to easily handle the requirements of high performance embedded applications, yet inexpensive enough to compete in the market for hi

Manufacturer:

NXP Semiconductors

Datasheet:

Part Number:

Description:

The Philips Semiconductors XA (eXtended Architecture) family of 16-bit single-chip microcontrollers is powerful enough to easily handle the requirements of high performance embedded applications, yet inexpensive enough to compete in the market for hi

Manufacturer:

NXP Semiconductors

Datasheet:

Part Number:

Description:

The XA-S3 device is a member of Philips Semiconductors? XA(eXtended Architecture) family of high performance 16-bitsingle-chip microcontrollers

Manufacturer:

NXP Semiconductors

Datasheet:

Part Number:

Description:

The NXP BlueStreak LH75401/LH75411 family consists of two low-cost 16/32-bit System-on-Chip (SoC) devices

Manufacturer:

NXP Semiconductors

Datasheet:

Part Number:

Description:

The NXP LPC3130/3131 combine an 180 MHz ARM926EJ-S CPU core, high-speed USB2

Manufacturer:

NXP Semiconductors

Datasheet:

Part Number:

Description:

The NXP LPC3141 combine a 270 MHz ARM926EJ-S CPU core, High-speed USB 2

Manufacturer:

NXP Semiconductors

Part Number:

Description:

The NXP LPC3143 combine a 270 MHz ARM926EJ-S CPU core, High-speed USB 2

Manufacturer:

NXP Semiconductors

Part Number:

Description:

The NXP LPC3152 combines an 180 MHz ARM926EJ-S CPU core, High-speed USB 2

Manufacturer:

NXP Semiconductors

Part Number:

Description:

The NXP LPC3154 combines an 180 MHz ARM926EJ-S CPU core, High-speed USB 2

Manufacturer:

NXP Semiconductors

Part Number:

Description:

Standard level N-channel enhancement mode Field-Effect Transistor (FET) in a plastic package using NXP High-Performance Automotive (HPA) TrenchMOS technology

Manufacturer:

NXP Semiconductors

Datasheet: