bt848kpf ETC-unknow, bt848kpf Datasheet - Page 54

bt848kpf

Manufacturer Part Number

bt848kpf

Description

Single-chip Video Capture For Pci

Manufacturer

ETC-unknow

Datasheet

1.BT848KPF.pdf

(141 pages)

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

BT848KPF

Manufacturer:

PHI

Quantity:

6 222

Part Number:

BT848KPF

Manufacturer:

BT

Quantity:

20 000

- Current page: 54 of 141

- Download datasheet (851Kb)

F

Video and Control Data FIFO

44

UNCTIONAL

FIFO Data Interface

D

ESCRIPTION

Loading data into the FIFO can begin only when valid pixels are present during the

even or the odd field. The pixel DWORD PD[31:0] is stored in FI[31:0], and the

video control code STATUS[3:0] is stored in FI[35:32]. The VBI data will be in-

cluded in the captured sequence if VBI capture capability is enabled.

and the state of the video timing unit (see Table 9). Video timing and control infor-

mation are passed through the FIFO along with the data stream. The FIFO buffer

isolates the asynchronous video input and PCI output domains. Control of the in-

put stream can only occur from the video timing unit of the video decoder and from

the configured registers. The interaction and synchronization of the DMA Control-

ler and the RISC instruction sequence will rely solely on the output side of the

FIFO.

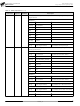

Table 9. Status Bits

lowed by pixel data. The FIFO Mode Indicator is to be stored in the FIFOs at the

beginning of every capture-enabled field, when the data format is changed

mid-field such as transitioning from packed VBI data to planar mode, and when

video capture of a field is asynchronously enabled. The mode status codes are al-

ways stored in planar format. FIFO1 receives two copies of the status code, while

FIFO2 and FIFO3 each receive one copy.

is the first pixel DWORD for the scan line. The EOL code is packed in the FIFO

with the last valid pixel data byte, which is the last DWORD location written to the

FIFO for the scan line. The EOL code indicates one to four valid bytes. The

VRE/VRO code is stored in the FIFO at the end of a capture-enabled field. The

DMA controller activates the appropriate PCI byte enables by the time a given

DWORD arrives on the output side of the FIFO.

Status[3:0]

The four bits of STATUS are used to encode information about the pixel data

Capturing data to the FIFO always begins with a FIFO mode indicator code fol-

The SOL code is packed in the FIFO with the first valid pixel data byte, which

0110

1110

0010

0001

1101

1001

0101

0100

1100

0000

FM1

FM3

SOL

EOL

EOL

EOL

EOL

VRE

VRO

PXV

L848A_A

Description

FIFO Mode: packed data to follow

FIFO Mode: planar data to follow

First active pixel/data DWORD of scan line

Last active pixel/data DWORD of scan line, 4 Valid Bytes

Last active pixel/data DWORD of scan line, 3 Valid Bytes

Last active pixel/data DWORD of scan line, 2 Valid Bytes

Last active pixel/data DWORD of scan line, 1 Valid Byte

VRESET following an even field–falling edge of FIELD

VRESET following an odd field–rising edge of FIELD

Valid pixel/data DWORD

Single-Chip Video Capture for PCI

Bt848/848A/849A

Brooktree

®

Related parts for bt848kpf

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Manufacturer:

ETC-unknow

Datasheet:

Part Number:

Description:

Manufacturer:

ETC-unknow

Datasheet: