EVAL-AD7612CBZ Analog Devices Inc, EVAL-AD7612CBZ Datasheet - Page 28

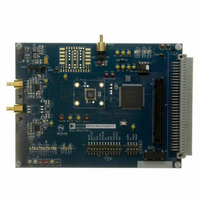

EVAL-AD7612CBZ

Manufacturer Part Number

EVAL-AD7612CBZ

Description

BOARD EVALUATION FOR AD7612

Manufacturer

Analog Devices Inc

Series

PulSAR®r

Specifications of EVAL-AD7612CBZ

Number Of Adc's

1

Number Of Bits

16

Sampling Rate (per Second)

750k

Data Interface

Serial, Parallel

Inputs Per Adc

1 Single Ended

Input Range

±5 V, ±10 V

Power (typ) @ Conditions

205mW @ 750kSPS

Voltage Supply Source

Analog and Digital

Operating Temperature

-40°C ~ 85°C

Utilized Ic / Part

AD7612

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

AD7612

External Clock Data Read After/During Conversion

It is also possible to begin to read data after conversion and

continue to read the last bits after a new conversion has been

initiated. This method allows the full throughput and the use of

a slower SDCLK frequency. Again, it is recommended to use a

*A DISCONTINUOUS SDCLK IS RECOMMENDED.

SDCLK

SDOUT

*A DISCONTINUOUS SDCLK IS RECOMMENDED.

SDCLK

CNVST

SDOUT

BUSY

BUSY

SDIN

CS

CS

Figure 43. Slave Serial Data Timing for Reading (Read Previous Conversion During Convert)

t

t

31

31

t

t

16

16

X*

X*

Figure 42. Slave Serial Data Timing for Reading (Read After Convert)

t

t

32

32

1

1

t

t

31

31

t

SER/PAR = 1

D15

SER/PAR = 1

D15

X15

33

2

2

D14

D14

X14

3

3

EXT/INT = 1

EXT/INT = 1

t

Rev. 0 | Page 28 of 32

35

t

34

t

D13

X13

37

15

t

36

4

t

35

t

37

D1

INVSCLK = 0

INVSCLK = 0

t

16

14

36

discontinuous SDCLK whenever possible to minimize potential

incorrect bit decisions. For the different modes, the use of a slower

SDCLK such as 20 MHz in warp mode, 15 MHz in normal mode

and 13 MHz in impulse mode can be used.

D0

D2

X2

X*

15

RD = 0

RD = 0

D1

DATA = SDIN

X1

16

X*

D0

X0

t

27

17

X*

X15

Y15

X*

18

X14

Y14

X*

19