MC908AP32CFAE Freescale Semiconductor, MC908AP32CFAE Datasheet - Page 164

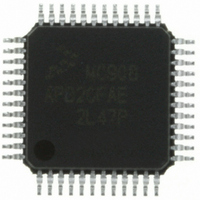

MC908AP32CFAE

Manufacturer Part Number

MC908AP32CFAE

Description

IC MCU 32K FLASH 8MHZ 48-LQFP

Manufacturer

Freescale Semiconductor

Series

HC08r

Specifications of MC908AP32CFAE

Core Processor

HC08

Core Size

8-Bit

Speed

8MHz

Connectivity

I²C, IRSCI, SCI, SPI

Peripherals

LED, LVD, POR, PWM

Number Of I /o

32

Program Memory Size

32KB (32K x 8)

Program Memory Type

FLASH

Ram Size

2K x 8

Voltage - Supply (vcc/vdd)

2.7 V ~ 5.5 V

Data Converters

A/D 8x10b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

48-LQFP

Controller Family/series

HC08

No. Of I/o's

32

Ram Memory Size

2KB

Cpu Speed

8MHz

No. Of Timers

2

Embedded Interface Type

I2C, SCI, SPI

Rohs Compliant

Yes

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

MC908AP32CFAE

Manufacturer:

Freescale Semiconductor

Quantity:

10 000

Company:

Part Number:

MC908AP32CFAER

Manufacturer:

Freescale Semiconductor

Quantity:

10 000

- Current page: 164 of 324

- Download datasheet (4Mb)

Serial Communications Interface Module (SCI)

11.4.3.4 Framing Errors

If the data recovery logic does not detect a logic 1 where the stop bit should be in an incoming character,

it sets the framing error bit, FE, in SCS1. A break character also sets the FE bit because a break character

has no stop bit. The FE bit is set at the same time that the SCRF bit is set.

11.4.3.5 Baud Rate Tolerance

A transmitting device may be operating at a baud rate below or above the receiver baud rate.

Accumulated bit time misalignment can cause one of the three stop bit data samples to fall outside the

actual stop bit. Then a noise error occurs. If more than one of the samples is outside the stop bit, a framing

error occurs. In most applications, the baud rate tolerance is much more than the degree of misalignment

that is likely to occur.

As the receiver samples an incoming character, it resynchronizes the RT clock on any valid falling edge

within the character. Resynchronization within characters corrects misalignments between transmitter bit

times and receiver bit times.

Slow Data Tolerance

Figure 11-7

or a framing error. The slow stop bit begins at RT8 instead of RT1 but arrives in time for the stop bit data

samples at RT8, RT9, and RT10.

For an 8-bit character, data sampling of the stop bit takes the receiver

9 bit times × 16 RT cycles + 10 RT cycles = 154 RT cycles.

With the misaligned character shown in

the count of the transmitting device is

9 bit times × 16 RT cycles + 3 RT cycles = 147 RT cycles.

The maximum percent difference between the receiver count and the transmitter count of a slow 8-bit

character with no errors is

For a 9-bit character, data sampling of the stop bit takes the receiver

10 bit times × 16 RT cycles + 10 RT cycles = 170 RT cycles.

With the misaligned character shown in

the count of the transmitting device is

10 bit times × 16 RT cycles + 3 RT cycles = 163 RT cycles.

164

shows how much a slow received character can be misaligned without causing a noise error

RECEIVER

RT CLOCK

MC68HC908AP Family Data Sheet, Rev. 4

MSB

Figure

Figure

Figure 11-7. Slow Data

154 147

------------------------- -

154

–

11-7, the receiver counts 154 RT cycles at the point when

11-7, the receiver counts 170 RT cycles at the point when

×

100

SAMPLES

=

DATA

4.54%

STOP

Freescale Semiconductor

Related parts for MC908AP32CFAE

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet: